����X�y�A�i�̉��

|

|

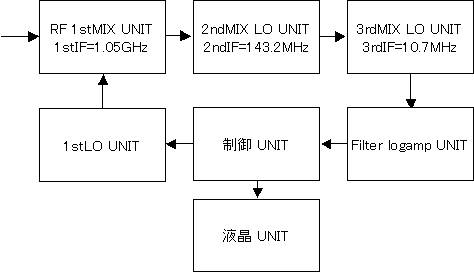

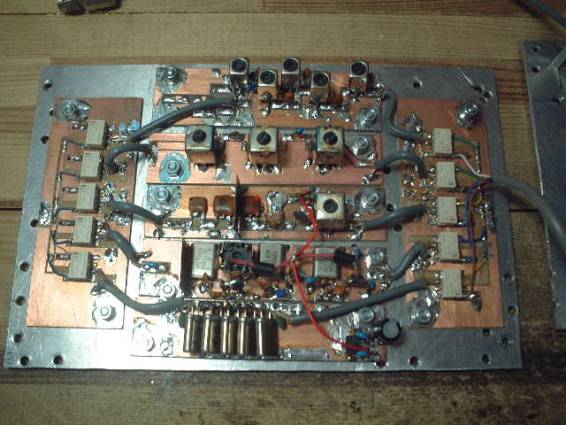

�S�̂̍\���}�ł��B |

�e���̐����ł����A�ŏ��ɐ���UNIT����������܂��B

|

|

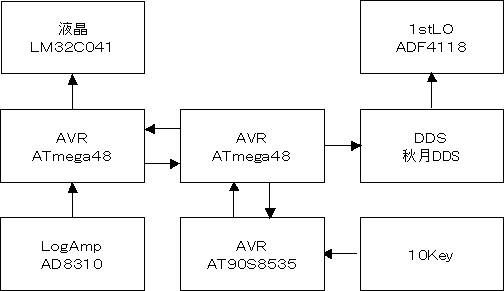

����UNIT�S�̗̂l�q�ł��B �v���O���� �f�[�^�\���E�P�OKey����i�`�s90�r�W�T�R�T�j �`�smega48�́A�Q�VMH���̃N���b�N�œ������Ă��܂��B �Q�VMH���ɐ[���Ӗ��͖����A�莝���Ŋ�{�g�̍ō����g�� ���Q�VMH���̐����ł��B ���̃V�[���hBOX�̒��ɁA�H����DDS�������Ă��܂��B |

|

|

������� �@�c�c�r����p�̂`�s���������S�W���A�c�c�r�ɐM���o�͖��߂��o���܂��B �A�t������p�̂`�s���������S�W�ɁA�V�O�i���𑗂�܂��B �B�t������p�̂`�s���������S�W�͂k�����`��������̐M�����`�^�c�ϊ����ĐM�����x�ɂ���������`���܂��B �C�t������p�̂`�s���������S�W�́A�c�c�r����p�̂`�s���������S�W�ɕ`��I���̃V�O�i���𑗂�܂��B �D�Q�S�O���C�����J��Ԃ��܂��B �E�c�c�r����p�̂`�s���������S�W�́A�`�s�X�O�r�W�T�R�T�ɃV�O�i���𑗂萧��f�[�^�𑗐M�����܂��B �F��M�����f�[�^�ɕύX�i���S���g���A�X�p�����g���A�X�C�[�v���ԁj������f�[�^��ύX���Ė��@����J��Ԃ��܂��B |

|

|

�オ�ADDS����p��A�smega48�@���̉���LCD����p�� A�smega48�ł��B |

|

|

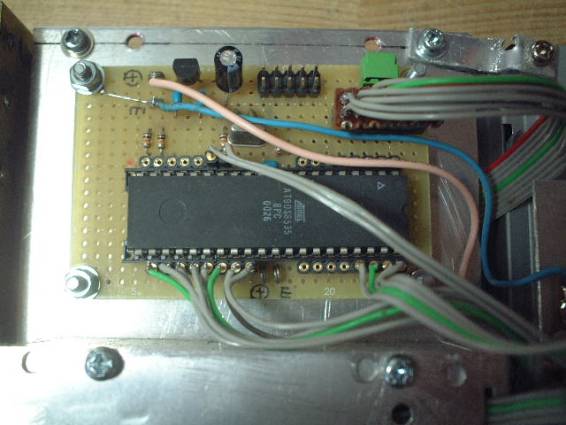

�P�OKey�A�P�U�~4�s��LCD�����AT�X�OS�W�T�R�T �ł��B |

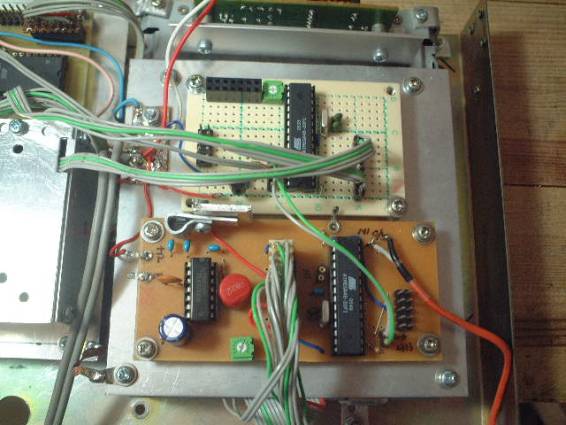

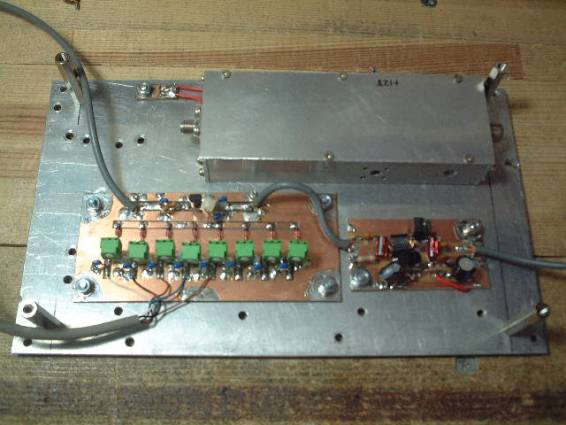

�e�����������ELogAmp�@UNIT

����UNIT�̓P�[�X�ɂ͓���Ă��܂���B

���̂܂܁A�d�����̏��2�i�d�˂Ŏ������Ă��܂��B

|

|

�ォ�� �TMH���@�K�E�V�����t�B���^ �PMH���@LC�t�B���^ �Q�O�OKH���@�Z���~�b�N�t�B���^�~3�i�{AMP �P�OKH���@�N���X�^���t�B���^�~3�i�{AMP �PKH���@5�f�q�N���X�^���@���_�[�t�B���^ ��ւ��ɂ́A�����[���g���Ă��܂��B |

|

|

��̃V�[���hBOX�̒��ɁAAD�W�R�P�O��LogAmp�� �����Ă��܂��B ���́APIN�_�C�I�[�h���g�������x���������{�P�O���� NFBAmp�ł��B |

|

|

LogAMP�ɂ́A�`�c�W�R�P�O���g���Ă��܂��B LogAMP�Ƃ����A�`�c�W�R�O�V���L���ł��B �`�c�W�R�O�V�́A�_�C�i�~�b�N�����W���|75�`+17dbm �܂ł�92db�ł����Ⴂ�����A���̃��x���ɂ���ɂ͂����Ƃ���ςł��B�i�ȑO�̎����j ���BAD603�Ƒg�ݍ��킹�ā|90dbm�܂Ŋg��ł��܂������荢��ł����d�����}�Q��ޕK�v�ɂȂ�܂��B �����ŁA�`�c�W�R�P�O����肵�Ďg���Ă��܂��B �O�i�ɁA�QSC1815�~�Q���g����NFBAmp��t���Ă��܂��B ����́A�S�̂̃Q�C�������̂��߂ł��B |

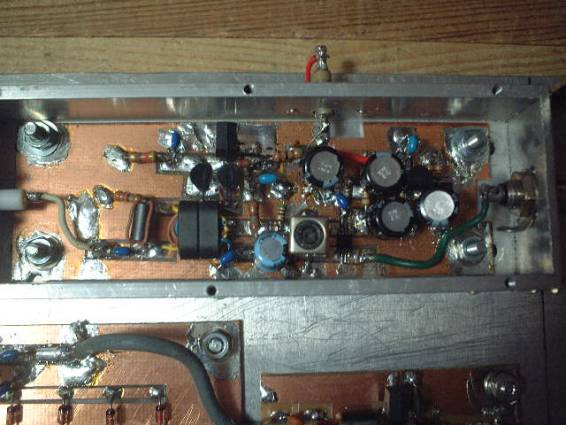

RF�E�P����MIX�@UNIT

|

|

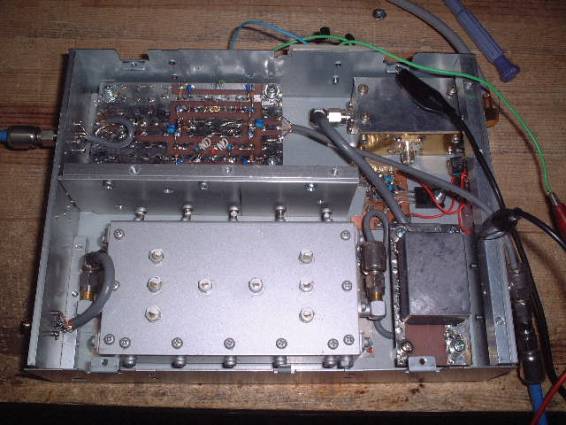

CDROM�̃P�[�X�ɓ���Ă��܂��B ����CDROM�́A�ŋ߃��T�C�N��SHOP��100�~�� ����ł��܂����T�C�Y�������Ȃ̂Ŏ�������Ƃ��� �ƂĂ��֗��ł��B �������A�g���ꍇ�̓A�[�X�̎����ɒ��ӂ��K�v�ł��B ���ATT�����t���Ă��܂��B ���͂�LPF�́A�T�O�OMH���łT�O�OMH����LPF�ƂP�O�O�OMH����LPF���ւ��Ă��܂��B ����́A�T�O�OMH������̐M���𑪒肷��Ƃ��ɂT�Q�TMH�����ɃX�v���A�X���ł邽�߂��̑�Ƃ��ē���Ă��܂��B |

|

|

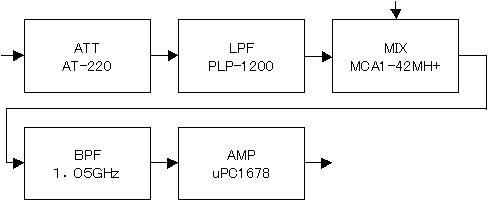

RF�E�P����MIX�@UNIT�̃u���b�N�}�ł��B �܂�AT-220�łP�O������������܂��B ATT�܂݂̂O�����\���̎��͎��͂P�O������������Ă��܂��B�|�P�O�����̎��������͂O�ł��B ���̌�ALPF��ʂ�MIX�ɓ���܂��B MIX�łP����Lo��MIX�����1.05GHz��BPF�ɓ��肻�̌�uPC1678�ő�������܂��B ���̃X�y�A�i�����Ƃ��A���ӂ����̂̓~�L�T�[�̑O�ŐM�����\���Ɍ��������ă~�L�T�[�̃��j�A��Ŏg�����̌�K�v�ȃ��x���܂ő�������Ƃ������Ƃł��B |

|

|

�����̗l�q�ł��B �M���͍��ォ�������U�̎������ɂ��������ō������� �o�͂���܂��B �a�o�e�ɂ́A���t�I�N�œ��肵�����̂��g���Ă��܂��� �}�L�d�C�̂R�Z�N�V�����̃L���r�e�B�ł��g���܂��B ����@LPF �E��@MIX�iMCA1�|�S�QMH+�j �E���@uPC1678 �����@�P�D�O�TGH���@BPF

SMA�R�l�N�^����̏����̎d���ł��B ����ł����SWR�̖\�ꂪ�Ȃ��Ȃ�܂����B |

�P����LO

|

|

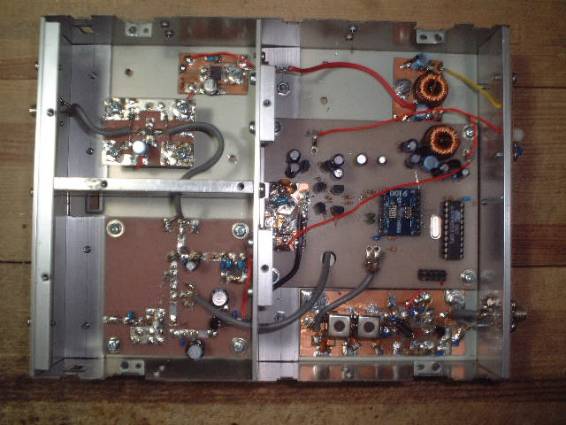

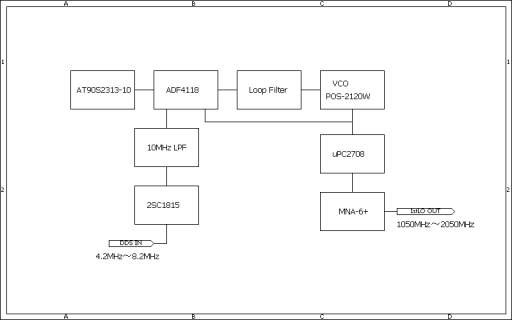

�����̗l�q�ł��B �E�̍L���Ƃ��낪�AADF4118���g����PLL���䕔�ł��B �������AVCO�iPOS-2120W�j�{uPC2708 ���オ�AMNA-6+ |

|

|

�P����LO�̃u���b�N�}�ł��B PLL�̐���ɂ́AADF4118���g���Ă��܂��B DDS�̏o�͂́A�P/10����ĂS�Q�OKH���`�W�Q�OKH���ɂȂ�܂��B VCO�iPOS-2120W�j�̏o�͂�1/2500����ĂS�Q�OKH���`�W�Q�OKH���ɂȂ�܂��B DDS���PHz�����ƁAVCO�͂Q�T�OH�������܂��B �P�X�C�[�v�͂Q�S�O�|�C���g�ɂ��Ă��܂��̂ŁA�Q�T�OHz�~�Q�S�O���U�OKH���ƂȂ�ŏ��X�p���͂UKH��/div�ɂȂ�܂��B |

|

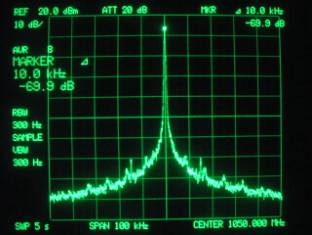

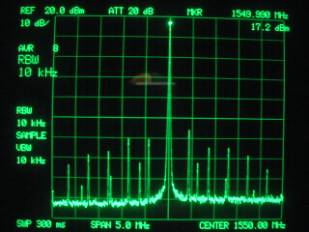

�c�c�r�o�́@�S�D�QMH�� �u�b�n�@�n�t�s�@�P�O�T�OMH�� |

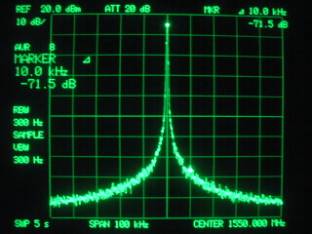

�c�c�r�o�́@�T�D�Q�l�g�� �u�b�n�@�n�t�s�@�P�T�T�OMH�� |

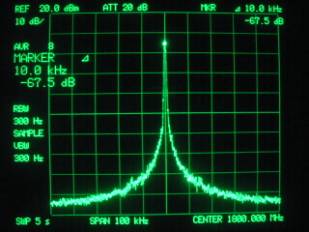

�c�c�r�o�́@�V�D�QMH�� �u�b�n�@�n�t�s�@�P�W�O�OMH�� |

|

|

|

|

|

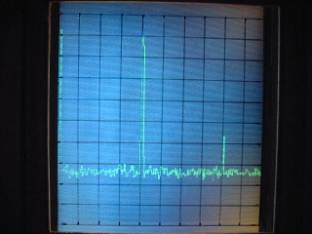

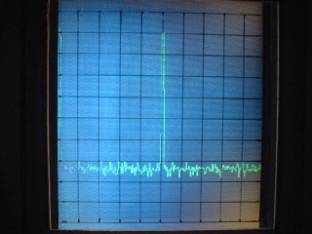

�r�r�a�ʑ��G���@�|�X�R�������^�g�� �i�P�OKH���@�I�t�Z�b�g�j |

�r�r�a�ʑ��G���@�|�X�S�D�U�������^�g�� �i�P�OKH���@�I�t�Z�b�g�j |

�r�r�a�ʑ��G���@�|�X�O�D�U�������^�g�� �i�P�OKH���@�I�t�Z�b�g�j |

|

|

|

|

|

���t�@�����X���[�N |

���t�@�����X���[�N |

���t�@�����X���[�N |

�s�q�S�P�V�Q�̍ō�������g�����A�P�W�O�OMHz�܂łȂ̂łQ�O�T�OMHz�͑���o���Ȃ��B

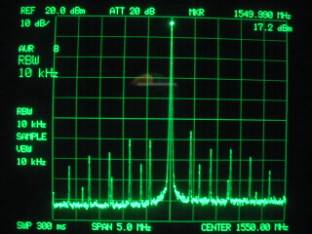

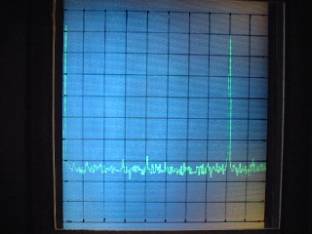

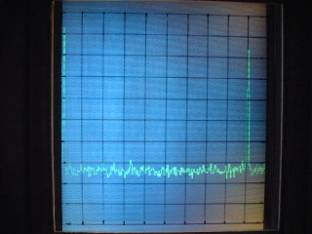

���t�@�����X�̃X�v���A�X���Ђǂ��ł��B

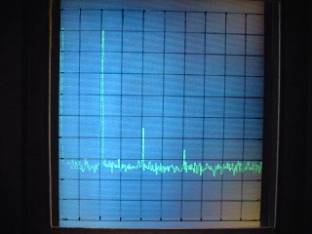

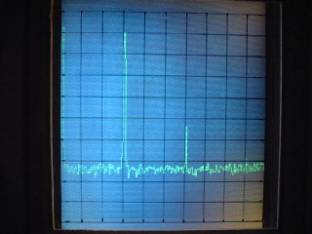

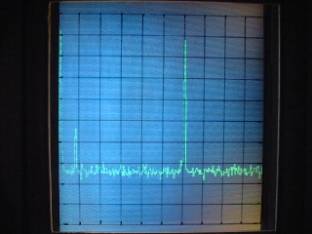

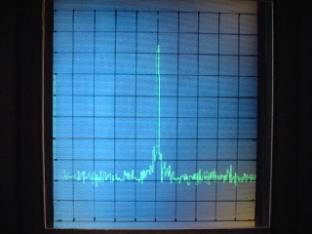

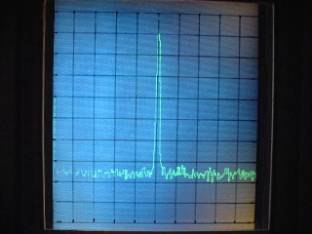

���ǂ��̃X�v���A�X���A�X�y�A�i�摜��ł��X�v���A�X�Ƃ��Č���܂��B

���̃X�v���A�X�����炷�悤�ɁA���[�v�t�B���^������Ƒ����X�C�[�v�^�C���ł͒ǐ����Ȃ��Ȃ�܂��B

����̃��[�v�t�B���^�́A�œK�̂��̂ł͂Ȃ��Ǝv���܂����A����ȏ���P�ł��܂���ł����B

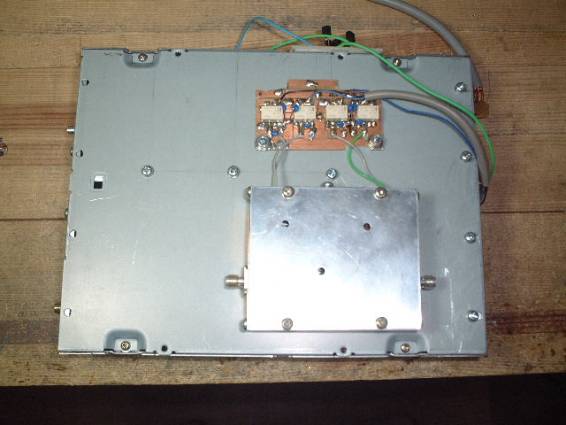

�Q�����l�h�w�E�Q�����h�e�@�R�����l�h�w�E�R�����h�e�@�Q�����k�n�E�R�����k�n

|

|

�����̗l�q�ł��B �E�ォ��A�Q�����l�h�w�i�l�b�P�R�P�S�R�j ���̍����A�P�S�R�D�QMH��BPF�{�`�����i�QSC3355�j ���̉��ɁA�P�S�R�D�QMH��BPF ���̉E�����A�R�����l�h�w�i�Q�r�j�P�Q�T�~�S�j�{LPF ��ԉ����A�R�����h�e�i�Q�r�j�P�Q�T�~�Q�j�{�k�o�e �ŏ��́A 2ndMIX+2ndIF+2ndLO 3rdMIX+3rdIF+3rdLO �Ƃ����悤�ɃP�[�X�ɓ���Ă��܂������A���ƂȂ������炠���肪�T�O�O�l�g�����ɏo��X�v���A�X�̔������̂悤�ȋC�����Ăk�n�Ƃl�h�w�{�h�e�Ƃ����悤�ɕ����Ă݂܂������X�v���A�X�͉�������܂���ł����B �i����́A�܂������̌����Ⴂ�ł����j ��H�}�͌��̂�����̉�H�}�ł��B |

|

|

������ɂ́A�Q�����k�n�C�R�����k�n���܂Ƃ߂Ă��܂��B ���̃V�[���h�ň͂��Ă���̂��A�Q�����k�n�̂o�k�k����p�̂`�c�e�S�P�P�V�ł��B �v���O�����̑薼���`�c�e�S�P�P�W�ɂȂ��Ă��܂����ǂ�����g���Ă������v���O�����łn�j�ł��B �`�c�e�S�P�P�V�̍ō����g���͂P�Q�O�O�l�g���ł��肬��ł������Ȃ��g���܂��B |

|

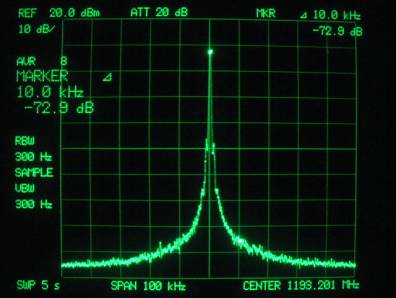

�Q�����k�n�@�P�P�X�R�D�Q�l���� |

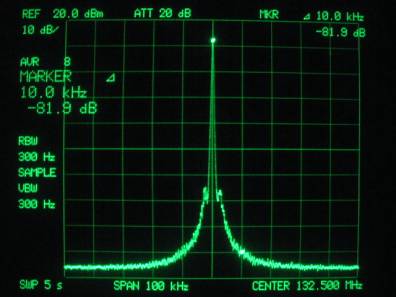

�R�����k�n�@�P�R�Q�D�T�l�g�� |

|

|

|

|

�r�r�a�ʑ��G���@�|�X�U�������^�g�� �i�P�OKH���@�I�t�Z�b�g�j |

�r�r�a�ʑ��G���@�|�P�O�T�������^�g�� �i�P�OKH���@�I�t�Z�b�g�j |

|

|

����p�l���ʂł��B �ŏ��́A���[�^���[�G���R�[�_���g���Đݒ�l��ω�������\��ł������A���[�^���[�G���R�[�_�̕ω��ɉ�ʕ\�����ǐ��o���Ȃ��̂łP�O�L�[�̓��͂����ɂ��Ă��܂��B ���������삵���炢�̂ŁA�L�[���Q�Ă���̂łt�o�E�c�n�v�m�Ƃ��ĉϏo����悤�ɂ��悤�Ǝv���Ă��܂��B �i�����ς݁j ���̂܂݂́A�E���̓��̓R�l�N�^�ׂ̗��`�s�s �^�����q�a�v �������u�a�v �ł��B �P�O�L�[�Őݒ�o����̂́A ���S���g�� �X�p�� �X�C�[�v���� �̂R�ł��B ��̉t����ʂ̕\���́A���ォ�璆�S���g���A�X�p���A�r�t�s�`�q�s���g���A�r�s�n�o���g�� �E�����A�X�C�[�v���Ԃł��B |

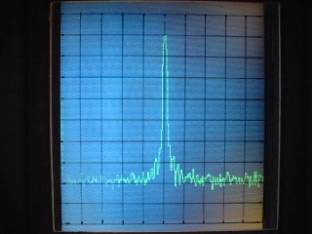

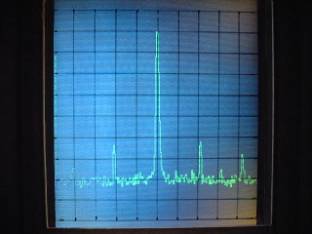

���̃X�y�A�i�̕\���ƁA�q�R�P�R�P�`�ł̕\�����r���Ă݂܂����B

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �P�O�OMH���@�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �Q�O�OMH���@�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �R�O�OMH���@�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �S�O�OMH���@�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �T�O�OMH���@�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �U�O�OMH���@�O������ �T�O�OMH����LPF�̓��������܂����߂T�Q�TMH�����̃X�v���A�X�������o�Ă��܂��B |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �V�O�OMH���@�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �W�O�OMH���@�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �X�O�OMH���@�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �R�O�OMH���@�{�P�O������ �ǂ��ɂ��A�{�P�O�������̓��͂܂Ŋϑ��\�ɂȂ�܂����B |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �R�O�OMH���@�|�P�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �R�O�OMH���@�|�Q�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �R�O�OMH���@�|�R�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �R�O�OMH���@�|�S�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �S�O�OMH���@�|�T�O������ |

|

|

|

SPAN=�P�O�O�OMH�� RBW=5MH�� �R�O�OMH���@�|�U�O������ |

|

|

|

SPAN���T�OMH�� RBW=�Q�O�OKH�� �P�OMH���@�O������ |

|

|

|

SPAN���T�OMH�� RBW=�Q�O�OKH�� �X�T�OMH���@�O������ ���̂�����̎��g���ɂȂ�ƁA���낢��ȗv�f�ɂ�� �w���l�����ۂ��Ⴍ�Ȃ��Ă��܂��B |

|

|

|

SPAN���Q�O�OMH�� RBW=�PMH�� �T�O�OMH���@�O������ |

|

|

|

SPAN���Q�OMH�� RBW=�Q�O�OKH�� �T�O�OMH���@�O������ |

|

|

|

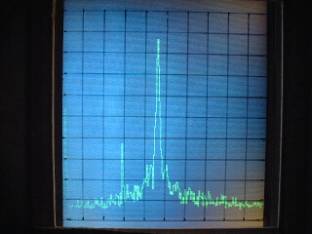

SPAN���QMH�� RBW=�P�OKH�� �T�O�OMH���@�O������ �P����LO��PLL�̃X�v���A�X�����̂܂܃X�v���A�X�� �Ȃ��ĕ\������Ă��܂��B |

|

|

|

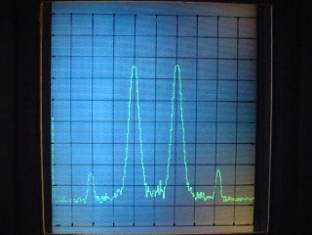

SPAN���Q�O�OKH�� RBW=�PKH�� �T�O�OMH���@�O������ �PKH���̃t�B���^�͒��S���g�����XKH������Ă��܂��B���̉e���Œ��S���g��������Ă��܂��B ��R�OKH�����ɃX�v���A�X������܂��B����́ALPF���T�O�OMH���Ő�ւ��Ă���e�����Ǝv���܂��B ���̑��̎��g���i�T�O�OMH���ȊO�j�ł͏o�܂���B |

|

|

|

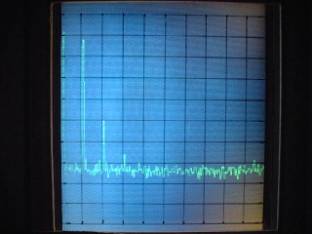

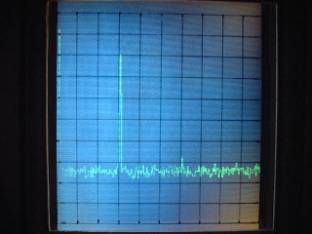

50.0MH����50.1MH���́|�P�O�������̂Q�M������͂����Ƃ��ł��B�ǂ��������ATT�͂Q�O�����ł��B���[�J�[����ATT�������IF�i�ő������ĕ\�����x�����ω����Ȃ��悤�ɂȂ��Ă��܂����A����ł͑Ή����Ă��Ȃ��̂ŕ\�����P�O����������܂��B �i����ł́A�펞�P�O������ATT�������Ă��܂��j ����X�y�A�i��RBW�͂P�OKH�� |

|

|

|

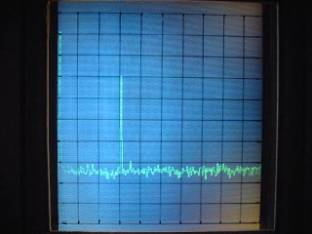

50.0MH����50.1MH���̂O�������̂Q�M������͂����Ƃ��ł��B IMD�̎R�����ۂ�荂���\������܂��B ����́A�g���Ă���MIX�̐��\�̍����낤�Ǝv���܂��B |

�Q�l����

PLL��H�̐v�Ɛ���

�g���C�_���E�R�A���p�S��

GH������̍����g��H�v

LC�t�B���^�̐v�Ɛ���@�@�@�ȏ�@CQ�o�Ŏ�

�Q�lHP

JR1PWZ�@���������HP