�X�y�A�i�����

���̓x�A�X�y�A�i����蒼�����Ƃɂ��܂����B

�O�ɍ�����X�y�A�i�̖��_�Ƃ��āA

�@ �P�����k�n���t���[�����̂��ߋ��ш�̑��肪�o���Ȃ��B

�A �o�n�r�|�Q�P�Q�O�v�̏o�͎��g�������j�A�łȂ����ߎ��g���̓ǂݎ��덷���傫���B

�B �W�U�O�l�g���i�QndLO�j�̃X�v���A�X������B

�C �P���h�e���P�f�g���Ƃ������߁A�T�O�O�l�g���ƂP�f�g���Ńt���A���x�����㏸����B

���̖��_������܂����B

�@ �ɂ��ẮA�o�k�k�����Ă݂܂��B

�A �o�k�k�����邱�Ƃɂ�肩�Ȃ���P����錩���݂ł��B

�B 2ndLO���A�P�P�S�O�l�g���Ƃ��Ă݂܂��B

�C �P�����h�e���P�D�O�T�f�g���ɂ��܂��B�i����łT�T�O�l�g���̂݉e�����錩���݂ł��j

�܂��́A�P�����k�n�̂o�k�k������n�߂܂��B

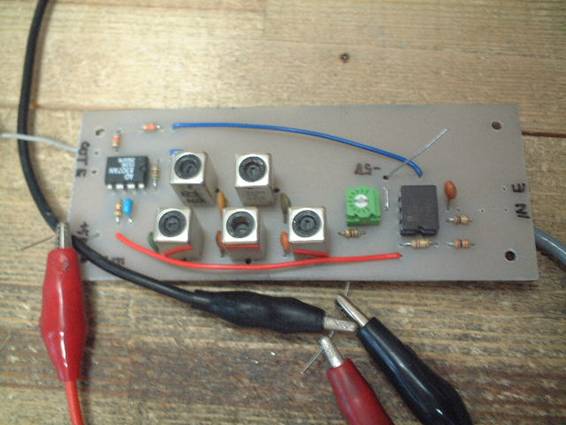

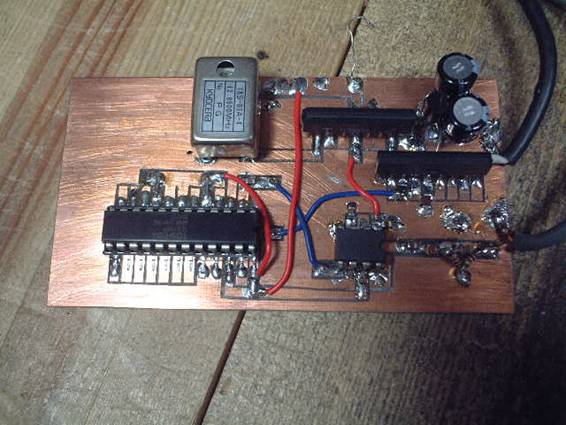

�o�k�k�h�b�ɂ́A�A�i���O�f�o�C�[�X�̂`�c�S�P�P�W���g���܂��B

�`�c�e�S�P�P�W�̃��t�@�����X�Ƃ��āA�S�D�Q�l�g���`�W�D�Q�l�g�����c�c�r������͂��܂��B������P/�P�O���Ċ�M�����S�Q�O�j�g���`�W�Q�O�j�g���Ƃ��܂��B

�o�n�r�Q�P�Q�O�̏o�͂́A�m�������łP/�Q�T�O�O���܂��B�P�O�T�O�l�g�����Q�T�O�O���S�Q�O�j�g���A�Q�O�T�O�l�g�����Q�T�O�O���W�Q�O�j�g���ƂȂ�P�O�T�O�l�g���`�Q�O�T�O�l�g��

���o�͂���܂��B�c�c�r���P�g���ω�����ƁA�Q�T�O�O�g���ω����邱�ƂɂȂ�܂��B

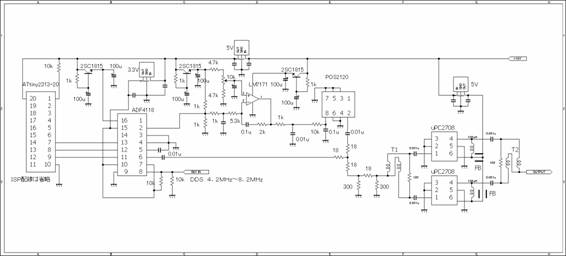

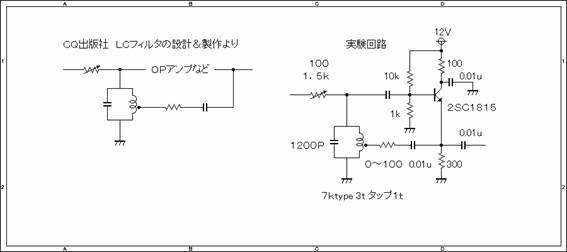

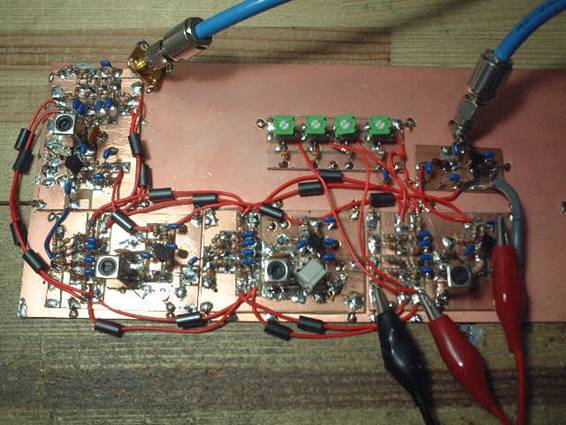

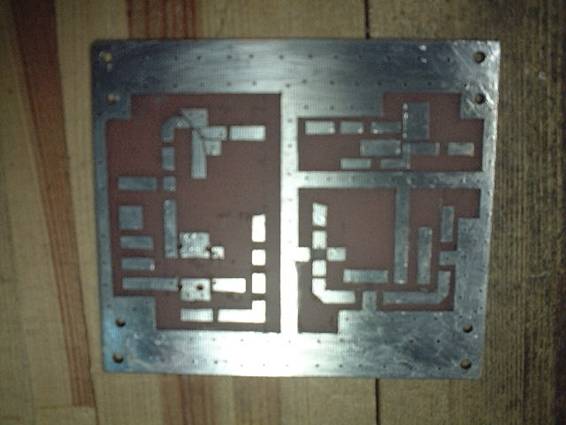

��H�}�ł��B�i�N���b�N�Ŋg�債�܂��j

|

�i�`�u�q�̂h�r�o�z���͏ȗ����Ă��܂��j �`�c�e�S�P�P�W����v���O�����i�`�stiny2313-20�j |

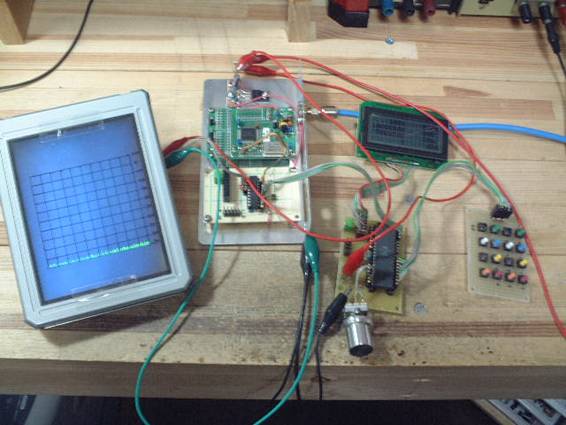

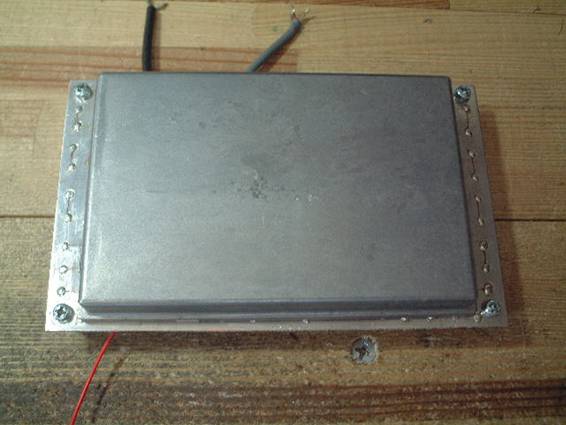

������A�b�c�|�q�n�l�̃P�[�X�ɓ���Ă݂܂����B���g��S������ĂP�����̃A���~�ŃV���[�V�����܂����B

���̂b�c�|�q�n�l�̃P�[�X�͓S���̂悤�ł����A�傫���������Ȃ̂Ō�ŃP�[�X�ɓ����Ƃ��y�����ł��B

�i���T�C�N���V���b�v��10�T�~�ł����j

|

|

|

|

|

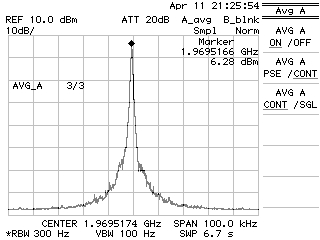

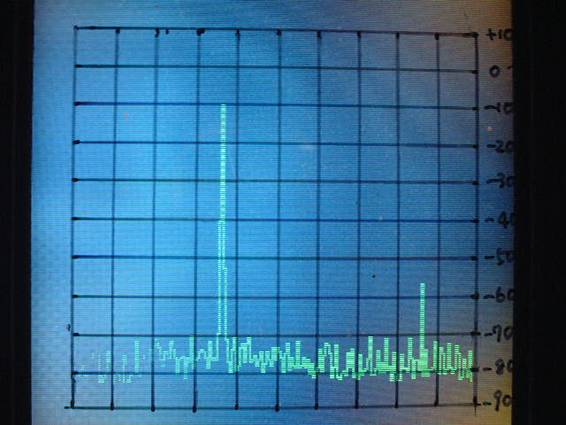

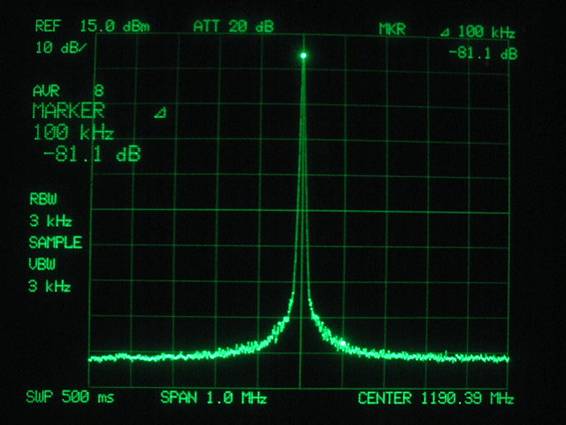

�Q�f�g���t�߂̃X�y�N�g���ł��B �ʑ��G���́A�P�O�j�g���I�t�Z�b�g�Ł|�X�P������/�g���ł��B �o�n�r�Q�P�Q�O�̃J�^���O�l�́[�X�U������/�g���ł��̂ł����������P���o�������ł��B |

|

|

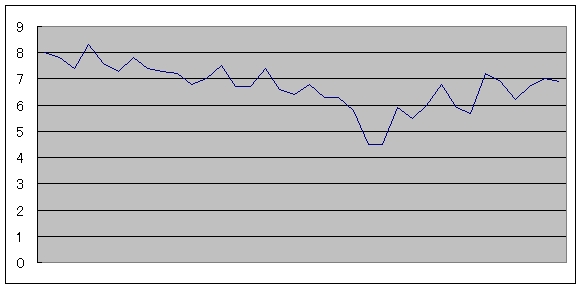

�P�D

�O�T�f�g���`�Q�D�O�T�f�g���܂ł̏o�̓��x���ł��B �P�D

�U�f�g���t�߂Ƀf�B�b�v������܂������̂Ƃ��댴���s���ł��B ���̂܂܂ł́A�������x���s���Ȃ̂ŕʂ̃f�o�C�X�F���ł��B UPC1677,uPC1678���g���Ă݂܂������P�D�T�f�g�������ŃQ�C���s���ō���̗p�r�ɂ͕s�������Ƃ������Ƃ�����g���܂���ł����B |

���_

�@ �o�͂��ш���ŕ��R�łȂ��B

�A �o�̓��x�������������~�����B�i�{�P�T�������j�@�i�@�A���ĐV�����f�o�C�X�������j

�B �k�������t�B���^�̒萔�̍œK���B�i����́A���ɂc�c�r���܂߂đS�̂Ƃ��Č����j

�l�m�`�|�U

�~�j�T�[�L�b�g�Ђ�Monolithic Amplifier�ɂl�m�`�|�U�Ƃ����h�b������܂��B

�O�D

�T�f�g���|�Q�D�T�f�g���Ł{�P�T�������ȏ�̏o�͂�����Ƃ���܂��B

����A�������肵�Ă݂܂����B�@�@�f�[�^�[�V�[�g

|

|

��Ɏ��������Ƃ���ł��B �h�b�{�̂́A��R�����p�Ƃ��Ȃ菬�����ł��B �d���́A�Q�D�W�u�A�T�u�Ƃ���܂����T�u�ɂ���Ǝ������@�������̂����U���~�܂�܂���B���������͂�����ƂO�������̓��͂Ł{�Q�O�������̏o�͂�����܂��B �����œd�����R�D�R�u�ɗ��Ƃ��Ăo�����V����o�����W�ւ̂R�R���� �P�O�O���Ɋ����Ă݂��Ƃ��딭�U�͎~�܂�܂����B ���̎��̎��g�����������̐}�ł��B |

|

|

���͂O������ �d���@�R�D�R�u�@�W�OmA �P�f�|�Q�f�g���Ł{�P�S�������ȏ�o�͂��Ƃ�܂����B ���g���������قڃt���b�g�ł��������ł��B |

�t���\����

�\���ɂ́A�r�g�`�q�o�̃p�b�V�u�J���[�t�����W���[���k�l�R�Q�b�O�S�P�i�̏H���ɔ����Ă����j���`�u�q�Ő��䂵�Ă݂悤�Ǝv���܂��B

�`�u�q�͂`�smega�S�W�|�Q�O���Q�V�l�g���̃N���b�N�œ������Ă݂܂��B�i�Q�V�l�g���ɐ[���Ӗ��͂���܂���B�莝���̐����̒��ŁA��{�g�ň�Ԕ��U���g���̍����̂����̂Q�V�l�g���̐����ł��j

|

��H�}�ł��B�i�N���b�N�Ŋg��j �i�h�r�o�z���͏ȗ����Ă��܂��j �t���̃o�b�N���C�g�ɂ́A�H���Ŕ����Ă����A�Ɋǁ{�C���o�[�^�Z�b�g �̃C���o�[�^�������g���Ă��܂��B�i�����炠����́A�O��̃X�y�A�i�\�����ƈꏏ�ł��B�j |

�k�l�R�Q�b�O�S�P�Ƃ`�smega�S�W�Ƃ̌����\

|

�k�l�R�Q�b�O�S�P |

�`�smega�S�W |

|||

|

�o�h�m�@�m�� |

�L�� |

�@�\ |

�o�h�m�@�m�� |

�o�n�q�s |

|

1 |

VSYNC |

���������M�� |

�P�W |

�o�a�S |

|

2 |

HSYNC |

���������M�� |

�P�X |

�o�a�T |

|

3 |

VSS |

�O�����h |

|

|

|

4 |

DCK |

�h�b�g�N���b�N |

�P�T |

�o�a�P |

|

5 |

VSS |

�O�����h |

|

|

|

6 |

DISP |

�c�r�o�@�n�e�e�M�� |

|

|

|

7 |

VDD |

���W�b�N�d���i�{�T�u�j |

|

|

|

8 |

VEE |

�t���쓮�d���i�{�R�O�u�j |

|

|

|

9 |

VSS |

�O�����h |

|

|

|

10 |

R1 |

�ԐF�f�[�^ |

�P�S |

�o�a�O |

|

11 |

R2 |

�Q |

�o�c�O |

|

|

12 |

R3 |

�R |

�o�c�P |

|

|

13 |

G1 |

�ΐF�f�[�^ |

�S |

�o�c�Q |

|

14 |

G2 |

�T |

�o�c�R |

|

|

15 |

G3 |

�U |

�o�c�S |

|

|

16 |

B1 |

�F�f�[�^ |

�P�P |

�o�c�T |

|

27 |

B2 |

�P�Q |

�o�c�U |

|

|

18 |

B3 |

�P�R |

�o�c�V |

|

|

19 |

VR1 |

�O�t���ϒ�R�p �i�P�O�j���j |

|

|

|

20 |

VR2 |

|

|

|

|

|

�J���[�p�^�[����\���������Ƃ���ł��B �`�u�q�Ƃa�����������g���āA�t���ɉ�ʕ\�������邱�Ƃ��o���܂����B �\�����x���C�ɂȂ�܂������A�X�y�A�i��ʕ\�����镪�ɂ͖��Ȃ� �������Ɗ����Ă��܂��B |

������A���ɃX�y�A�i�̉�ʕ\���p�ɉ��H���܂��B

�k�l�R�Q�b�O�S�P�́A���R�Q�O�h�b�g�A�c�Q�S�O�h�b�g�ŏ�̂P�Ԗڃ��C���̍�����E�ɂR�Q�O�h�b�g�\�������ɂQ�Ԗڃ��C����\�����E�E�Q�S�O�Ԗڃ��C���̉E�[�łP��ʕ\����

�I���܂��B

���낢��l�����̂ł����A��ʂ������Ŏg���̂���Ԃ����̂ł����A��������ƃv���O���������G�ɂȂ��Ă`�u�q���a�`�r�b�n�l�i�c�d�l�n�Łj�̗e�ʓ��Ɏ��߂�̂�����

�ł��B

�����ʼn�ʂ��c�Ɏg�����Ƃɂ��܂��B�P�����k���̂P�X�C�[�v�ƂP��ʕ\���������A�P���C�����Ƃɓ����Ă����M���̋����ɍ��킹�Đ�����������ƃX�y�A�i�̕\����

�o����̂ł͂Ƃ����l���ł��B

|

|

���̍l�����Ńv���O����������ĕ\�������Ă݂܂����B �c�c�r�@�|�@���색�_�[�t�B���^�@�[�@�`�^�c�ϊ��@�\�@�t���\�� �c�c�r�͏H���̂c�c�r���g���Ă��܂��B �o�͂͂S�D�Q�l�`�W�D�Q�l����������o�͎��g���̐ݒ���ȒP�Ȃ̂Ŏg���܂��B �i���}�́A���S���g���P�O�D�U�X�T�l�g���@�r�o�`�m�P�O�j�g���j �c�c�r�ŏo�͂��A�t���ɐM���𑗂�܂��B�t���͂P���C���\������ �c�c�r�ɏI���̐M���𑗂�܂��B���̐M�����Ăc�c�r�͎��� �M�����o�͂��܂��B������Q�O�O���C�����J��Ԃ��I���ƍŏ��� �߂�܂��B ���̃v���O�����ł̕\�����x�́A�P�X�C�[�v��Q�O�O�����ʂł��B ���߂ĂP�O�O�������炢�ɂ͂��������̂ł����E�E ����̉ۑ�ł��B |

|

|

�������i�ł��B |

�h�e�t�B���^

�q�a�v�����߂�h�e�t�B���^�ł����A�ŏ��͂k�b�t�B���^�i�`�R�l�j�A�Z���~�b�N�t�B���^�i�P�O�j�`�R�O�O�j�j�A�N���X�^���t�B���^�i�P�j�`�R�j�j�ō�����ł�����

�b�p�o�ŎЂ́u�k�b�t�B���^�̐v������v�̒��ɂ���X�y�A�i�p�̂k�b�t�B���^�����������Ƃ���P�O�j�`�P�l���炢�܂ł͍�ꂻ���Ȋ��������Ă����̂�

�����������Ă݂邱�Ƃɂ��܂��B

|

|

������H�ł��B �n�o�A���v�ȂǂƂ���܂����A�Q�r�b�P�W�P�T���g���Ă݂܂����B |

1�i�ł̎������ʂł��B�i�G�~�b�^����̐��A�Ғ�R�͂O�I�[���j

|

���͒�R |

�R�����ш敝 |

�}������ |

���� |

|

�O�I�[�� |

�P�D�X�Q�l�g�� |

�|�T���� |

|

|

�P�O�O�I�[�� |

�P�D�T�U�l�g�� |

�|�U���� |

|

|

�T�O�O�I�[�� |

�T�W�O�j�g�� |

�|�P�Q���� |

|

|

�P�j�I�[�� |

�S�S�O�j�g�� |

�|�P�U���� |

|

|

�P�D�T�j�I�[�� |

�S�O�O�j�g�� |

�|�Q�O���� |

|

|

�Q�D�T�j�g�� |

�R�W�O�j�g�� |

�|�Q�Q���� |

|

���́A������Q�i�ڑ����āA�}��������U�p�ɂs���P�̃A���v�����Ă݂܂����B

|

���͒�R |

�R�����ш敝 |

�}������ |

���� |

|

�P�O�O�I�[�� |

�U�Q�O�j�g�� |

�|�P�T���� �i�E�}�̓A���v�ŕ������j |

|

|

�P�D�T�j�I�[�� |

�P�Q�O�j�g�� |

�|�Q�R���� �i���j |

|

�Q�i�\���ł��ꂭ�炢�̓������o��̂Ȃ�A�T�i���炢�ɂ���Ƃ�����̂ł͂Ǝv���܂��B

|

|

�S�i�\���ɂ��Ă݂܂����B ��H���A�QSC1815�̃G�~�b�^�ɓ����Ă���A�җʒ����p�̒�R �́A���������Ȃ�N���`�J���łO�D�T�I�[���ς���Ă��ш敝�����Ȃ�ω����܂��B �S�i���܂������A�萔�݂͂ȓ����ł����̒�R�l�͂R�O�I�[���O��Ŕ����Ɉ���Ă��܂����B �ꉞ�S�i�Ŏg���Ă݂āA����Ȃ��悤�Ȃ�����P�i����邱�Ƃɂ��܂��B �ш敝�͐v�l�Ƃ́A��������Ă��܂�������������̂ɓK���Ȓ�R���Ȃ��̂ł��̂܂g���Ă݂邱�ɂ��܂��B |

|

RBW |

���� |

SPAN�@=�@10MH�� |

SPAN�@=�@1MH�� |

|

�P�OK |

�P�SK |

|

|

|

�R�OK |

�R�W�� |

|

|

|

�P�O�OK |

�X�U�� |

|

|

|

�R�O�OK |

�R�T�U�� |

|

|

�Q�O�O�V�N�T���Q�U��

�����ŁA�P�O�j�g���̂q�a�v�Ŏ��p�ɂȂ�̂��O�ɍ�����X�y�A�i���g���ĂP�����k�n�i�o�k�k���j�ƁA�t���\�����u���g���Ď������Ă݂܂����B

|

|

�������i�ł��B �悭�A����Ȋ����œ����ȂƎ����ł����S���Ă��܂��܂��B |

|

|

�t���X�p�� �q�a�v���R�l�g�� SweepTime=200ms �R�T�O�l�g���@�|�P�O�������̐M������ꂽ�Ƃ���ł��B �i����@�u�E�t�g�e�p�r�f�g�p�j �g�����r�f�̑�Q�����g�́[�U�O���������Ȃ̂Ńm�C�Y�� ������Ă��܂��B �E�Ɍ�����̂́A��Q�k�n�i�W�U�O�l�g���j�̃X�v���A�X�ł��B |

|

|

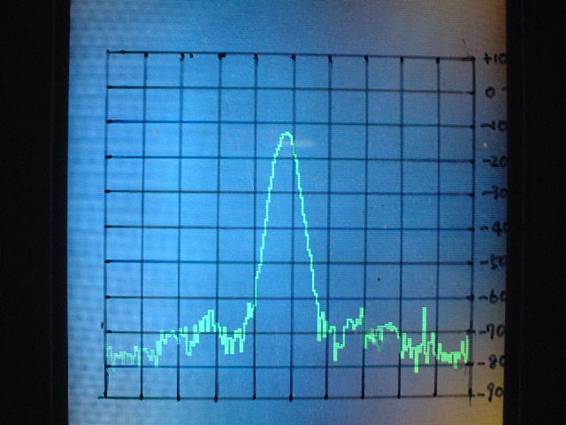

���}�́A��̐M���� �r�o�`�m���Q�O�O�j�g�� �r���������s���������T�O�O�������� �q�a�v���P�O�j�g�� �Ō������̂ł��B �����M���O���Ȃ��A���ꂢ�Ɍ����Ă��܂��B

|

���̒��q���ƁA�q�a�v���R�j�g���A�P�j�g�������ł͂Ȃ���������܂���B

�Q�O�O�V�N�U���V��

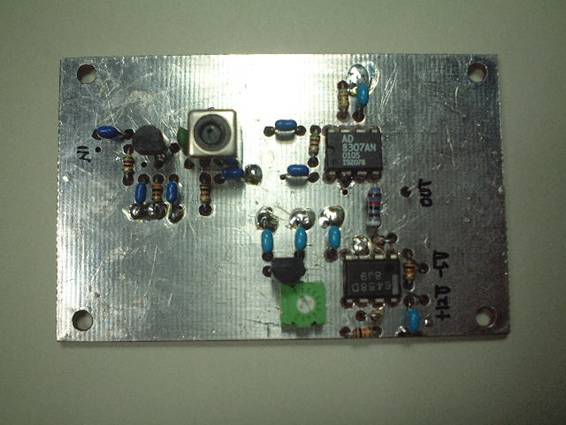

�����ɂ́A�`�c�W�R�O�V���g���܂��B

�`�c�W�R�O�V�̃f�[�^�V�[�g�ɂ́A�`�c�U�O�R�Ƒg�ݍ��킹�ă_�C�i�~�b�N�����W���g�傷����@���L���Ă���܂��B

|

|

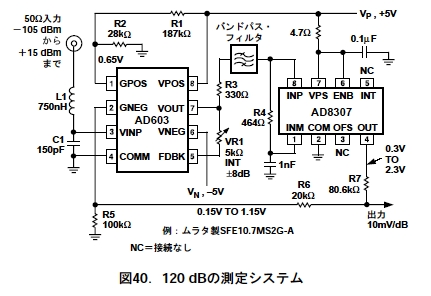

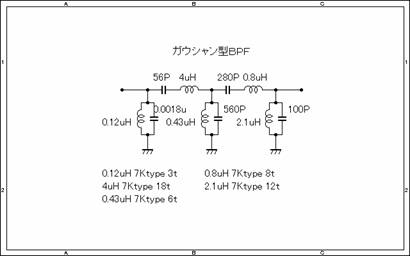

�i�`�c�W�R�O�V�@DataSheet���j �U�O�R�ƂW�R�O�V�̊Ԃɂa�o�e������Ă���܂��B ��������邱�Ƃɂ��A���j�A�̈悪�{�P�O����������]�P�O�O�������܂Ł{�|�P������ �Ԃɓ���悤�ɂȂ�܂��B���̃t�B���^�������ƒႢ����-�W�O�������܂ł����v���o���Ȃ��Ȃ�܂��B �����A�����ɋ����t�B���^����ꂽ�̂ł͂q�a�v������ȏ�L���o���Ȃ��Ƃ������ƂɂȂ�܂��B �����Ń��j�A�悪�����Ȃ�̂͊o��̏�ŁA�����ɂq�a�v���R�l�g���̃t�B���^�������ė��邱�Ƃɂ��܂��B ���̃t�B���^�́A�K�E�V�����^�̂a�o�e���g�����Ƃɂ��܂��B |

|

|

���}���A�K�E�V�����^�T���̂a�o�e�ł��B �萔�́A�u�k�b�t�B���^�̐v�Ɛ���v�b�p�o�ŎЂ��Q�l�ɂ��ē��������܂����B ������A��}�̂a�o�e�̏��ɓ���܂��B �C���s�[�_���X�͂T�O�I�[���Ōv�Z���Ă��܂��B �b�͋߂���̂������l�ɕς��Ă��܂��B |

|

|

|

�ш敝�́A��R�l�g���ɂȂ�܂����B �����A��̒萔�͑ш敝�S�l�g���Ōv�Z�������̂ł��B�ŏ��R�l�g���Ōv�Z�����萔�ł͂Q�l�g���̑ш敝�ƂȂ�܂����B �����͂悭����܂����̂܂g�����Ƃɂ��܂��B |

|

|

�v���Ԃ�ɁA�v�����g����G�b�`���O���č��܂����B +�P�O�������`�|�X�O�������܂ł̂P�O�O�����łقڃ��j�A�̓����������܂����B |

|

|

������́A�O�ɍ���Ă����`�c�U�O�R�̕ς��Ƀt�H���[�h�`�f�b�p�̂Q�r�b�Q�R�S�W���g�������̂ł��B �O�������`�|�X�O�������܂ł́A���j�A�ȓ������o���܂����B ������ɂ́A�i�Ԃ̃t�B���^������Ă���܂���B �t�B���^������Ƃ�����ł��P�O�O�����̃��j�A�悪�����ł������Ȋ����ł��B |

�Q�O�O�V�N�U���P�R��

�R�����k�n�{�l�h�w

|

|

�R�����k�n�ɂ́A�P�R�Q�D�T�l�g���̐������U���j�b�g������ł��܂����̂ł�����g�����Ƃɂ��܂����B �o�͂́{�P�O����������܂��̂łR�����̂`�s�s��ʂ��Ăs�t�e�|�P�ɓ���܂��B �l�h�w�̌�ɂ́A�Q�r�b�P�W�P�T�̂m�e�a�A���v��1�i����ă��X�����J�o�[���đS�̂łقڃQ�C���O�ɂ���\��ł����A���ۂ́{�P�D�T�����Q�C��������܂��B ��ŁA�Q�r�b�P�W�P�T�̂m�e�a�A���v�̒萔�����ăQ�C���O�ɂ��܂��B ����ŏ������g���W���ς��܂��B �Q�����h�e=10�D�V�l�g��+�P�R�Q�D�T�l�g��=�P�S�R�D�Q�l���� 2ndLO���o�k�k�̕�����̊W�łP�P�X�O�D�S�l�g���ɂȂ�܂��̂łP�����k�n�� �P�O�S�V�D�Q�l�g���|�Q�O�S�V�D�Q�l�g���܂ł��g�����ƂɂȂ�܂��B |

�O���������͎��̃X�v���A�X

|

|

|

�O���������͎��܂Ń��j�A���e�B�͊m�ۂ���Ă��܂��B �S�̂�ʂ��ĐM�����x���́A�O�������ȉ��ɂ��܂��̂ł���ł������ƂɂȂ�܂��B |

|

�O�|�T�O�O�l�g�� |

�O�|�Q�O�O�l�g�� |

|

�|�P�O���������͎��̃X�v���A�X

|

|

|

���̌�ɂq�a�v�̃t�B���^�����܂��̂� �X�v���A�X�͂��ꂢ�����ς薳���Ȃ��Ă����ł��傤�B |

|

�O�|�T�O�O�l�g�� |

�O�|�Q�O�O�l�g�� |

|

�Q�O�O�V�N�U���Q�O��

�Q�����k�n�{�l�h�w

�\���́A�o�k�k�ɂ͂s�b�T�O�W�P���g���܂��B

�ŏ��̕����ɂ͂s�c�U�P�Q�V�a�o���g���ĂP/�P�Q�W�i�P�P�X�O�D�S�l�g�����P�Q�W���X�D�R�l�g���j�ɂ��Ă��܂��B

���̂h�b�̍ő���g���͂P�f�g���ɂȂ��Ă��܂����P�D�Q�f�g���ł��g���Ă��܂��B

���̌�s�b�X�P�X�W�łP/�X�R�i�X�D�R�l�g�����X�R���P�O�O�j�g���j���ĂP�O�O�j�g�������o���܂��B

�ŏ��͂`�c�e�S�P�P�V���g���č���Ă��܂������A�����V�����Ă��܂��莝�����Ȃ��Ȃ����̂ŏ�L�̍\���ɂ��܂����B

�`�c�e�S�R�U�O�|�U�Ƃ����f�o�C�X�����肵�Ă����̂ł����A�����̖ړr���������ɂ�����߂Ă������}�ȍ\���Ƃ��܂����B

�P�P�X�O�D�S�l�g�������o���u�b�n�́A�H���Ŕ����Ă���l�p�b�R�O�X�|�P�O�P�U�i���U���g���͈́@�X�W�O�l�g���`�P�O�T�O�l�g���j���g���܂��B

�l�h�w�ɂ́A�~�j�T�[�L�b�g�̂q�l�r�|�Q���g���Ă��܂��B�q�e/�k�n�̎��g���͈͂͂T�|�P�O�O�O�l�ł�����薳���g���Ă��܂��B

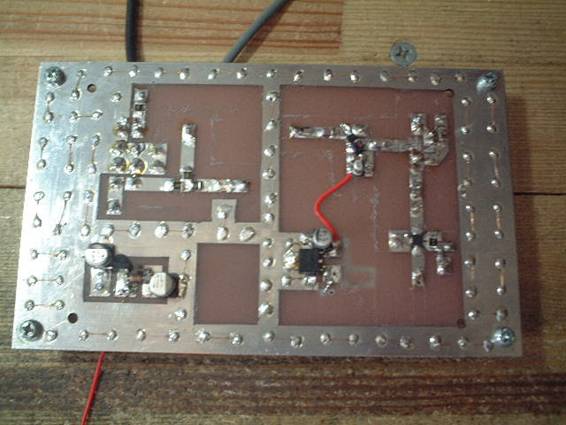

|

|

2ndLO�p�̂P�P�X�O�D�S�l�g���̂u�b�n���������܂��B �܂��́A�P�[�X�Ɏ~�߂Ă���n���_���͂����Ē��g�����o���܂��B ���̏㕔�����k�ɂ�����܂��B �����Ƀn���_���Ĕ��U���g�����������܂��B |

|

|

�n���_�����l�q�ł��B ����ʐ����āA���U���g�����P�P�V�O�l�g���`�P�Q�P�O�l�g���ʂ܂ʼnϏo����悤�ɂȂ�܂����B ��A�P�[�X�ɖ߂��Ɣ��U���g�����ς��܂��̂ŃR���g���[���d���̒��S�����ŖړI���g���ɂȂ�悤�ɒ������܂����B ���ꂾ���n���_��Ƃp��������̂��o�̓��x���͂��Ȃ艺����܂��B |

|

|

����������Ղł��B �������A�u�b�n�ƃ|�X�g�A���v�iuPC2710�j �E�オ�A�l�h�w�����ɂȂ�܂��B �E�����A�o�̓A���v�iuPC1651G�j�Ƃk�o�e �ł��B |

|

|

���i�����������Ƃ���ł��B |

|

|

�o�k�k���䕔�ł��B |

|

|

���͂ɂP�O�S�O�l�g���A�O�������̐M������͂����Ƃ��̏o�͂ł��B |

|

|

�u�b�n�̏o�̓X�y�N�g�����ł��B �P�O�O�j�g���I�t�Z�b�g�ŁA�ʑ��G���́|�P�P�S�D�Q������/Hz�ł��B |

�Q�O�O�V�N�U���Q�T��

�P�����k�n�̉��P

�P�����k�n�̏o�̓A���v���A�l�m�`�|�U�ɑւ��܂����B

|

|

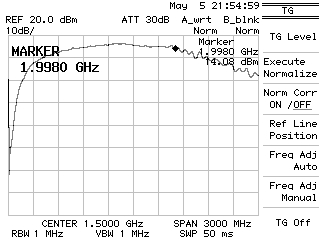

����V���ɍ��܂����B �\���� POS2120 -

uPC2708 - MNA-6�̍\���ł��B �Q�V�O�W�Ƃl�m�`�|�U�̊ԂɃf�o�C�_�����ĂP�����k�n�� ���o����悤�ɂ��܂����B �i�����s�f����鎞�ׁ̈j �l�`�w�g�n�k�c�@�\���g���ďo�̓��x���𑪂��Ă݂��Ƃ����}�̂悤�ɂȂ�܂����B |

�ш���ɓn���Ăقڕ��R�ȏo�́i��{�P�T�������j�邱�Ƃ��o���܂����B

|

|

�Ō�ɁA�V�[���h�P�[�X��킹�ďo���オ��ł��B |