SGの製作

AVRとDDSを使ってSGを製作しようと思います。

基本性能としては

発振範囲 1KHz〜60MHz

最大出力レベル +17dbm

最小設定周波数 1Hz (後ほど説明しますが、プログラムの制約で実際は1KHzが実用レベルだと思います)

発振周波数設定方法 ロータリーエンコーダ・キーボード入力

JA4FZQ/伊藤さんにアドバイスいただき1Hz単位まで設定できるようになりました。

クロック周波数は、31.999725MHz(実際の発振周波数)×6=191998350で設定しています。

|

|

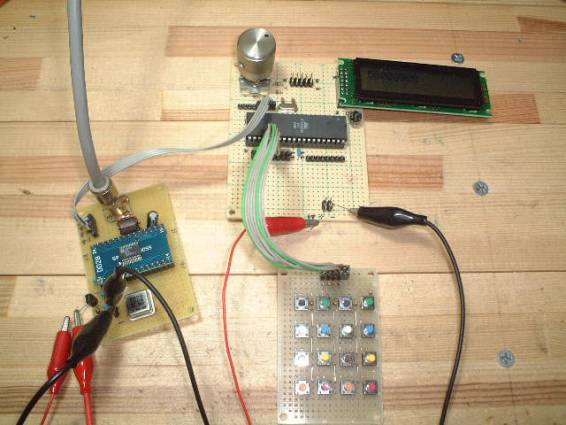

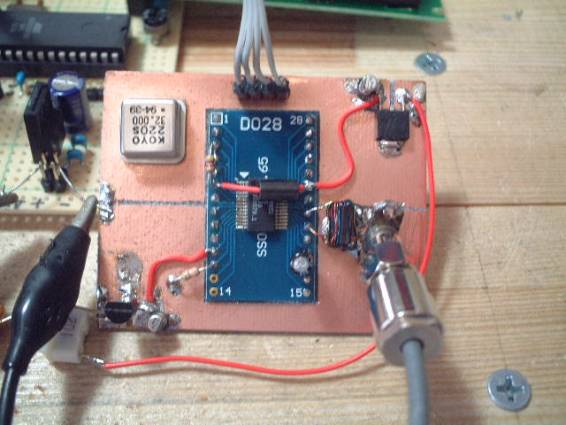

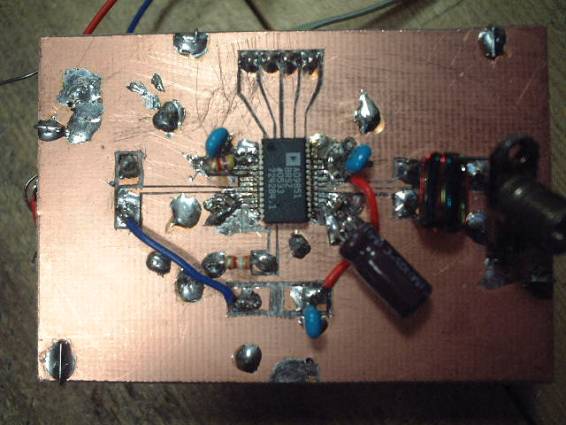

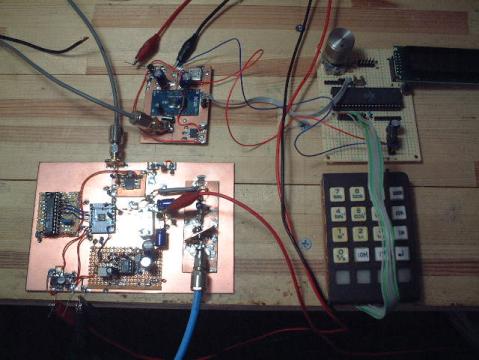

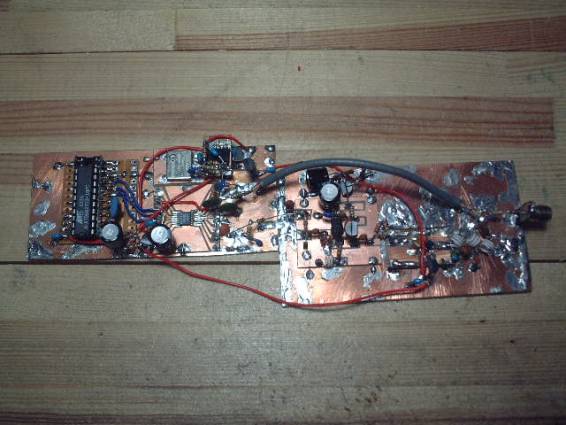

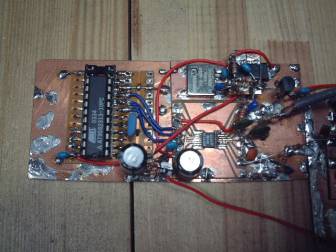

AVR・DDS・LCD・KBD・RE すべて繋げて実験している様子です。

|

|

|

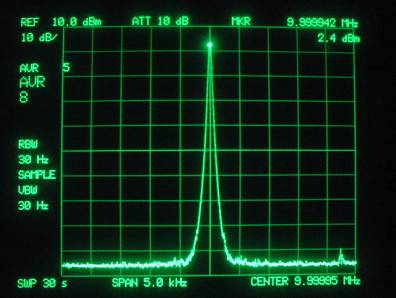

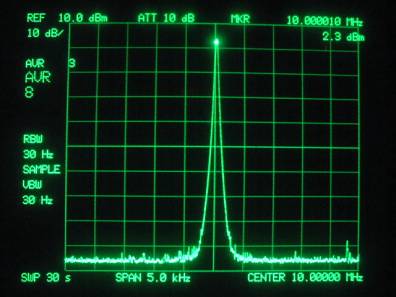

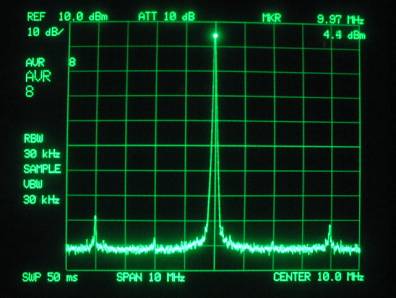

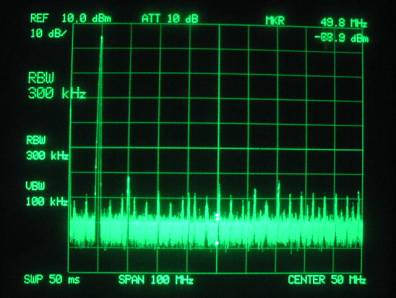

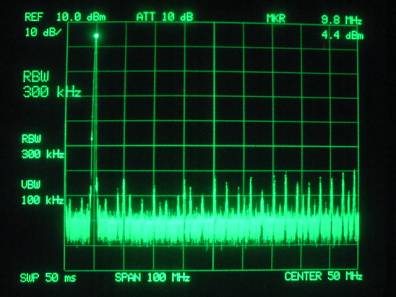

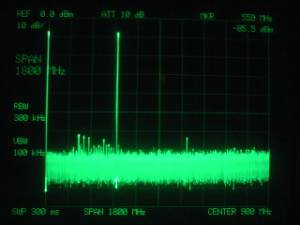

その時の、出力スペクトラムです。 (0−100MHz) |

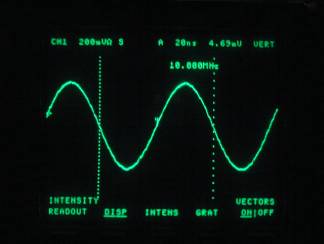

プログラムですが、起動直後は10MHzを出力します。

ロータリーエンコーダでの可変は1MHzにしてあります。

キーボード入力は、0〜9はそのまま数字入力10〜14は、ロータリーエンコーダの可変範囲の設定にしています。

10→10MHz単位

11→1MHz単位

12→100KHz単位

13→10KHz単位

14→1KHz単位 としています。

15は、エンター機能にしています。

キーボードからは、出力周波数を直接入力します。

|

|

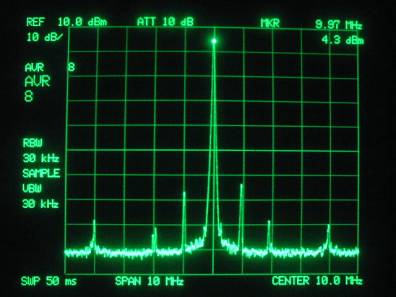

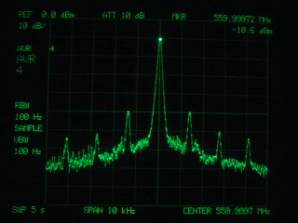

50MHz出力時の近傍の様子です。 13.6KHzのスプリアスがあります。 今のところ、どこから来ているのか判りません。 規則正しく並んでいるので何かの影響だろうとは思いますが不明です。 これを押さえ込めれば使えそうです。 |

AD9851を制御する、設定値は

設定値=(2の32乗÷クロック周波数)×出力周波数 で求めることが出来ます。

ここで2の32乗は、4294967296になります。

今回クロックは32MHzのクリスタルオシレータを使いましたので

4294967296÷(32000000×6)=22.36962133になります。

BASCOM BASICで小数点の演算の仕方が判らないので、プログラムではまず1000で割って22370を掛けています。

そのため、1KHz以下では誤差が大きくなります。

今回のSGは最低可変幅を、1KHzとすることでこの問題から逃避します。

Megaシリーズでは、浮動小数点演算が可能というような記事を見ましたがBASCOM BASICから使えるのか判りません。

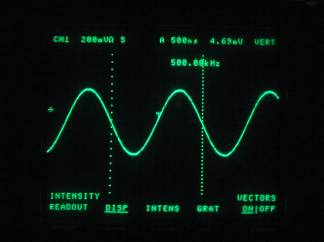

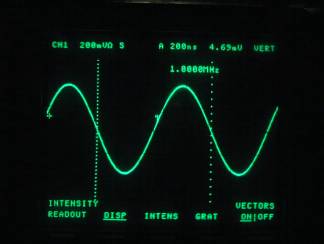

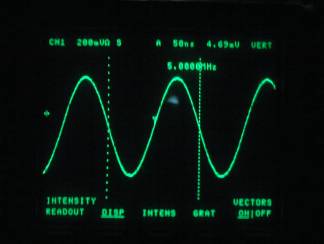

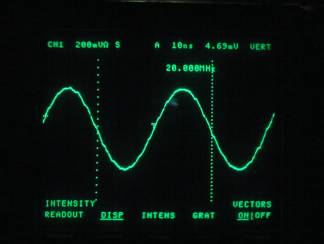

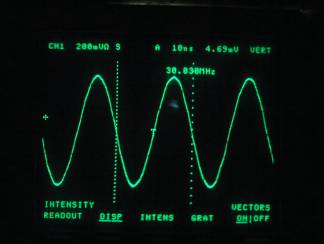

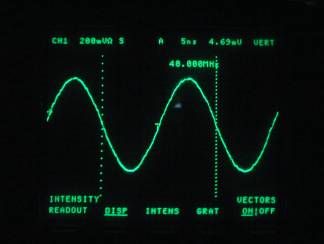

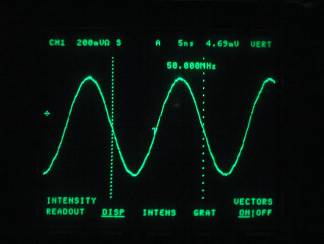

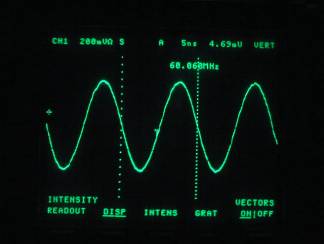

500KHz・1MHz・5MHz・10MHz・20MHz・30MHz・40MHz・50MHz・60MHzにおける

発振波形、高調波、C/Nの様子です。

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

発振周波数が、30MHzを超えるあたりから近傍スプリアスが増加します。

高調波はLPFを入れることにより除去出来ますが、低いほうのスプリアスは除去出来ません。

HPFと組み合わせたBPFが必要かもしれません。

データーシートによると

広帯域スプリアスなしのダイナミック・レンジ

1.1 MHzアナログ出力(DC 〜 72 MHz) 64 dBc

20.1 MHzアナログ出力(DC 〜 72 MHz) 53 dBc

40.1 MHzアナログ出力(DC 〜 72 MHz) 55 dBc

50.1 MHzアナログ出力(DC 〜 72 MHz) 53 dBc

70.1 MHzアナログ出力(DC 〜 72 MHz) 43 dBc

狭帯域スプリアスなしのダイナミック・レンジ

1.1 MHz(±50 kHz) 85 dBc

1.1 MHz(±200 kHz) 80 dBc

40.1 MHz(±50 kHz) 85 dBc

40.1 MHz(±200 kHz) 80 dBc

70.1 MHz(±50 kHz) 85 dBc

70.1 MHz(±200 kHz) 73 dBc

(AD9851 データーシートより抜粋)

広帯域のスプリアスは、ほぼデーターシートどうりですが、侠帯域で10〜20db悪化しています。(特に30MHz以上)

|

|

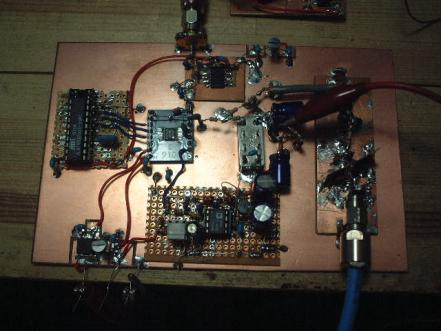

今回は、バラックセットではなく両面基盤を使って アナログ・デジタルグランドにも気を使って作った つもりです。 30MHz以上の近傍スプリアスの悪化の原因を 探さねばいけません。 |

その後、清水さんにアドバイスをいただきパスコンをピンすぐに付けたところかなりスプリアスが改善されました。

|

|

|

|

真中が、以前の特性です。右側が写真のとおりピンそばにパスコンを付けたときです。近傍スプリアスについてはかなり改善されました。

しかしC/Nはほとんど変化がみられません。

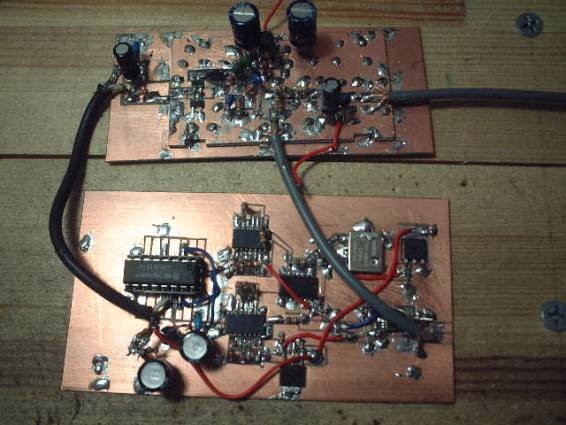

エクステンション基板を使ったのでは限界があると感じたので生基板をカッターナイフでカットして基板を作ってみました。

|

|

パスコンは出来る限りピンそばに付けました。 |

|

|

電源の配線は裏側を使っています。 |

|

今回作った基板 |

エクステンション基板 |

|

|

|

|

根元あたりが少しすっきりしたような感じです。 |

|

|

|

スプリアスが、かなりきれいになりました。 |

|

|

|

全体的にノイズが減少しました。 |

|

|

|

|

AD9851を使うにあたっては、パスコンの位置でスプリアスやサイドバンドノイズの出方がかなり変わります。

AD9851までは、カッターナイフを使ったお手手メーションでもなんとか工作が出来ました。

ここで、計画変更をします。

最初は、DDSを直接使って0−60MHzのSGを作るつもりでいましたが、DDSをPLLのリファレンスに使いVCOにPOS−535を

使って(現在430用SGに使ってある)0−500MHzくらいのSGを作る方向に計画変更です。

POS−535は、実測で275MHz〜570MHzくらいまで発振してくれるので、このうちの280MHz〜560MHzの280MHz間を

利用して、別に280MHzの信号源を用意してMIXすることで0−280MHzを取り出します。

280〜550MHzはそのまま使い0〜560MHzまでを取り出す計画です。

|

|

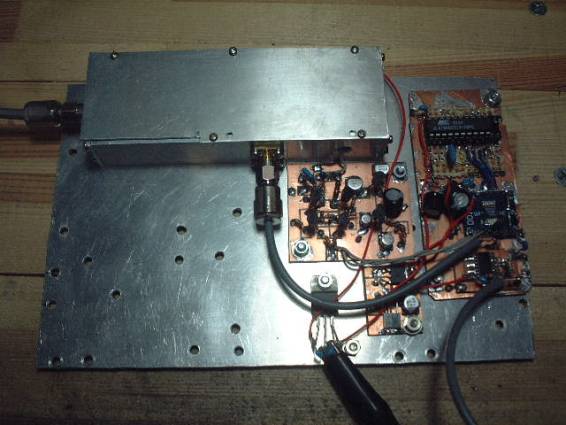

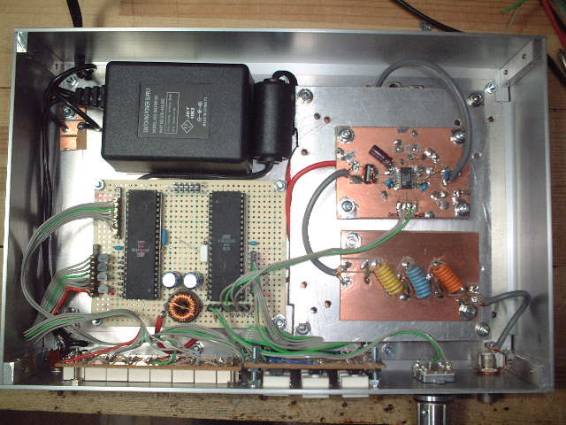

ということで、これまで作ってきたものを繋げて実験中です。

|

AVRは、PLL用がAT90S2313、DDS用がAT90S8535、PLL用ICはADF4117という構成です。

今回、PLLのループフィルタにはOPAMPを使ったアクティブフィルタを採用しました。アクティブフィルタは反転増幅器を利用したもの

なのでADF4117のPHASE DETECTOR POLARITYを、POSITIVEからNEGATIVEに変更しています。

ADF4117の比較周波数を100KHzにしました。

この関係で、DDS1MHzの変化でVCOは28MHz動きます。DDSを10MHz〜20MHzまで使って280MHz〜560MHz

が作れます。

ですからキーボードから直接入力した場合、28で割ってやるとDDSの設定値が求められます。

又、この設定値で判定してAVRから制御信号を取り出し、回路を切り替えてMIXを通すか直接出力するか決めます。

|

|

|

|

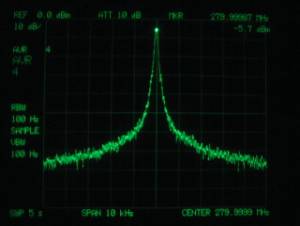

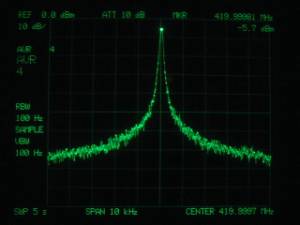

左から、280MHz・420MHz・560MHz 出力時の波形です。(SPAN 10KHz RBW=100Hz)

まだまだ、ループフィルタの定数が悪いようです

|

|

|

280MHz・560MHz出力時の広い範囲です。 |

|

|

|

280−560MhzのBPFを入れています。 |

280MHz PLL−LO

280MHzの、LOをADF4116を使って作りました。

|

|

生基盤の上に、組み立てています。 左側が、ADF4116とAT90S2313−10 と13MHzのXCOです。 右側が、2SK125を2本使ったVCOと uPC2709を使ったAMPで約+10dbmの 出力を得ています。 実際に使う場合は、しっかりとしたシールドBOXの 中に収納する予定です。 |

|

|

|

|

よく考えたら、280MHzをLOにするとこの出力がスプリアスとして残ります。

そこでLOを560MHzにすることにします。0−280MHzが逆になりますがそこはソフトで対応します。

560MHzのVCOには、現在TR技に連載中の「PLL周波数シンセサイザの設計法徹底解説」に掲載されている回路を参考にしました。

|

|

上が、VCO部 下が、PLL部 VCO部には、シールドケースをすっぽり かぶせます。 ADF4116の最高周波数が550MHzなので 今回は、4046を使いました。 |

基準信号源には13MHzのTCXOを使い74HC393で 1/8 1/13 して125KHzを取り出します。

VCOの出力は、uPB1507GVを使って1/128した後74HC393で 1/7 1/5 して125KHzを取り出しMC14046に入力しています。

|

|

シールドケースの中にPOS−535が入っています。 |

ADF4117のレファレンスカウンタを1/100に設定しています。

DDSが10MHz(POS535の出力280MHz)の時比較周波数は100KHzになります。

DDSが20MHz(POS535の出力560MHz)の時比較周波数は200KHzになります。

又、ADF4117のBカウンタを1/87 Aカウンタを1/16にして 32×87+16=2800となり

280MHz出力の時100KHz、560MHz出力の時200KHzの比較周波数となります。

|

|

POS−535(560MHz出力) |

自作560MHzVCO |

位相雑音 |

|

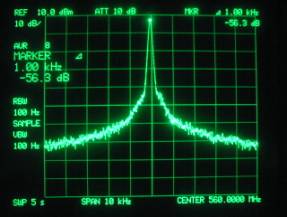

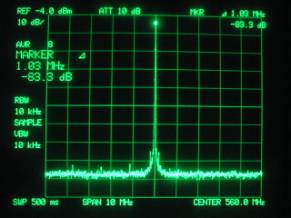

SPAN 10KHz |

|

|

(1KHz Offset) POS535(カタログ値)-75dbc/Hz 実測値 POS535 -77dbc/Hz 自作VCO -72dbc/Hz |

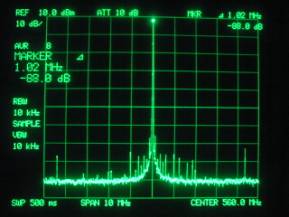

|

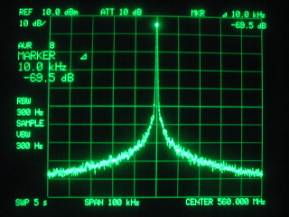

SPAN 100KHz |

|

|

(10KHz Offset) POS535(カタログ値)-95dbc/Hz 実測値 POS535 -93.1dbc/Hz 自作VCO -92.6dbc/Hz |

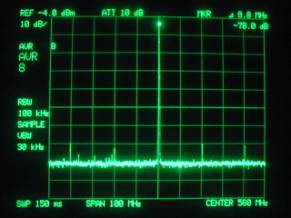

|

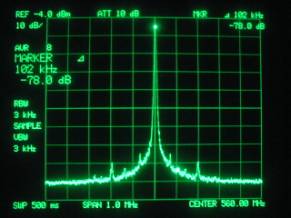

SPAN 1MHz |

|

|

(100KHz Offset) POS535(カタログ値)-116dbc/Hz 実測値 POS535 -111.1dbc/Hz 自作VCO -110.4dbc/Hz |

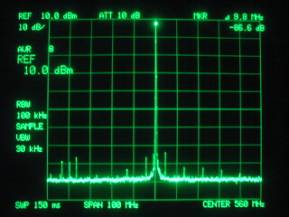

|

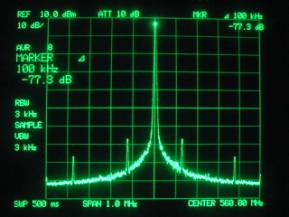

SPAN 10MHz |

|

|

(1MHz Offset) POS535(カタログ値)-137dbc/Hz 実測値 POS535 -121.1dbc/Hz 自作VCO -120.4dbc/Hz |

|

SPAN 100MHz |

|

|

|

|

|

|

|

|

POS535の出力波形で、比較周波数内につのがかなりあります。

現在のところどこで発生しているのか原因不明です。そのうちオニタイジしないといけません。

位相雑音は、POS535のデータシート上の数値とあまり変わりませんのでこんなものでしょう。

30MHz基準発信機

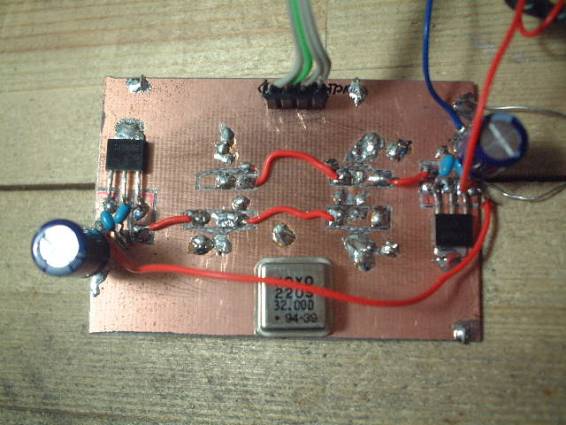

9851を使ったDDS用の基準信号源として、30MHzの基準発信機をつくりました。

|

|

10MHzのXCOを基準信号源に使い 4046を使ったごく平凡なVXO-PLL回路です。 |

|

|

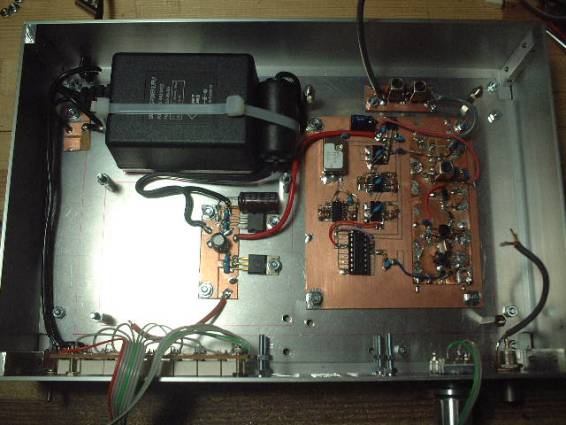

ケースにまとめだしました。 電源は、秋月で売っている1個200円の16V1Aの ACアダプターを使っています。 3端子Rgで12Vと5Vを作っています。 7SegLEDも秋月で売っている10個100円のアノード コモンです。 |

|

|

AVR基板、DDS基板、LPFを実装してほぼ完成です。 今回は、ATTやアイソレーションAMP等は内臓しませんでした。 これらは、別に作ったものがあるのでそれらを組み合わせて 使うことにします。 |