AD9952

2008.03.04

�A�i���O�f�o�C�[�X�́u�`�c�X�X�T�Q�v���������Ă݂܂����B

�i�q�P�o�v�y��������́A�A�h�o�C�X�����Ɏ������Ă݂܂����B

�`�c�X�X�T�S�@�f�[�^�V�[�g�@�i�X�X�T�S�ɂ́A���{��̃f�[�^�V�[�g������܂��B���e�͂قƂ�Ljꏏ�Ȃ̂ł�������g���܂����j

|

|

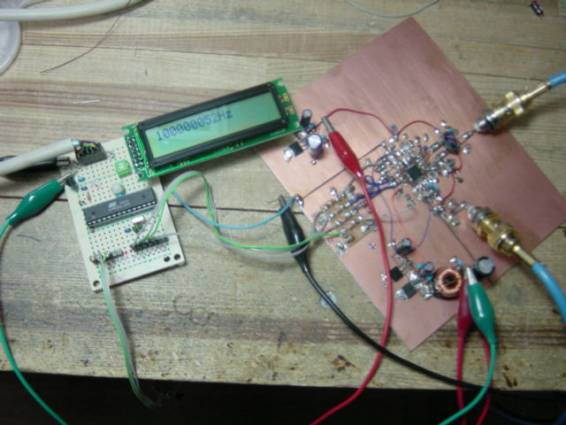

�܂��́A��ւ̎����ł��B ��������̂ɊۂP��������܂����B �A�i���O�ƃf�W�^���̃O�����h�͕������܂��B |

|

|

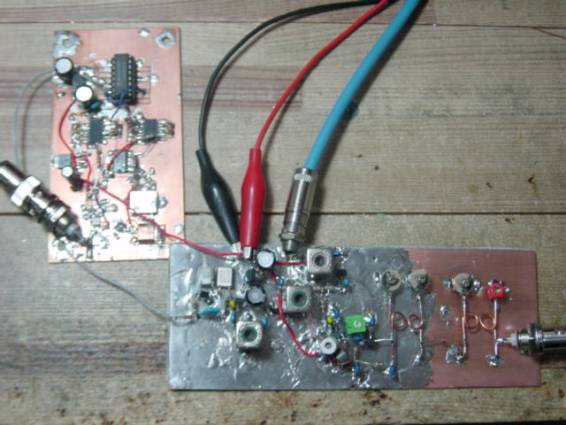

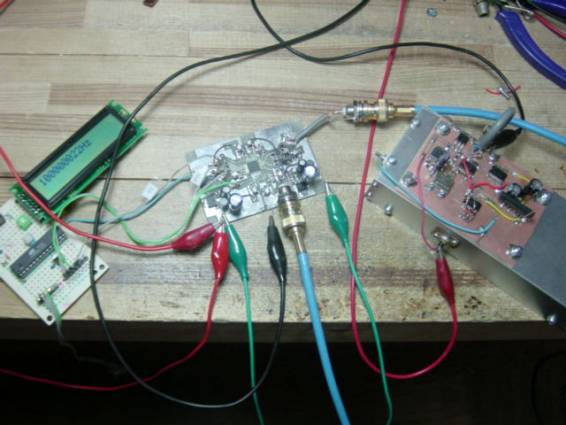

����̎������@�ł��B���ʊ���g���܂����B �\�ʂ̓������A�`�c�X�X�T�Q�̑傫�����T�����قǑ傫������ �܂��B�����Ă��̒����ɂS�����p�̌����J���ĂO�D�P�����̐^�J�� ���`�c�X�X�T�Q�̗��̃����h�Ƀn���_�t�����č��������Ŋ�̓� ���ʂɃn���_�t�����܂����B �������ĕ\�ʂ̃A�i���O�O�����h�ɃX���[�z�[���Őڑ����܂����B ��������Ɠ������@�ł�낤���Ƃ��v���܂������ɕ����Ă��� ���Ƀn���_�t�����鎩�M������܂���ł����B �������邱�Ƃɂ��`�c�X�X�T�Q�̑��͊�ɂ������Ă���̂ŏ��� �͂������Ă����S�ł��B |

�ŏI�I�ɂ́A�`�u�q�Ő��䂵�����̂ł����܂����h�������Ȃ��̂ŃA�i�f�o�̂g�o���琧��\�t�g�Ɛڑ���H���_�E�����[�h���Ă��܂����B

����\�t�g�i�ڑ���H�j�@���̒��ŁA�����̊��ɂ��������̂��_�E�����[�h���Ă��܂��B

|

|

����������������Ղł��B |

|

|

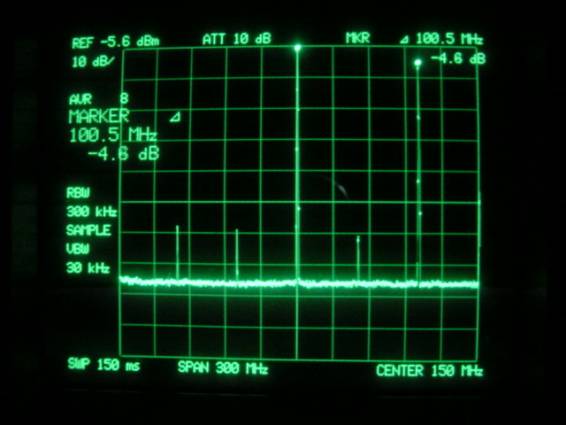

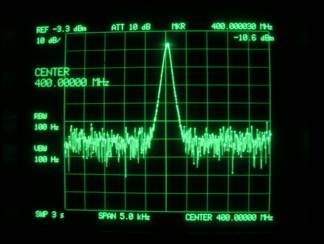

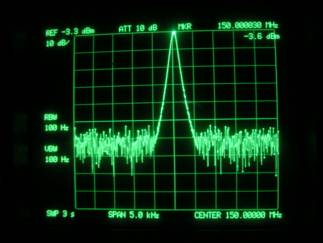

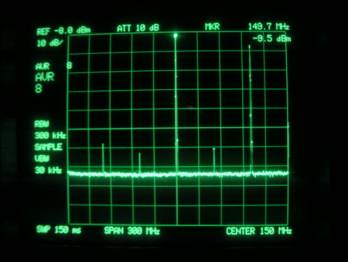

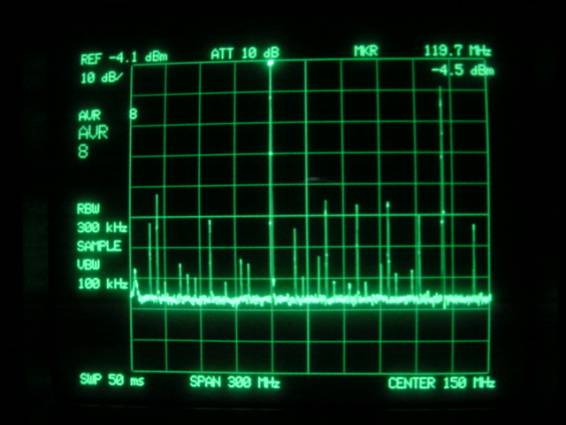

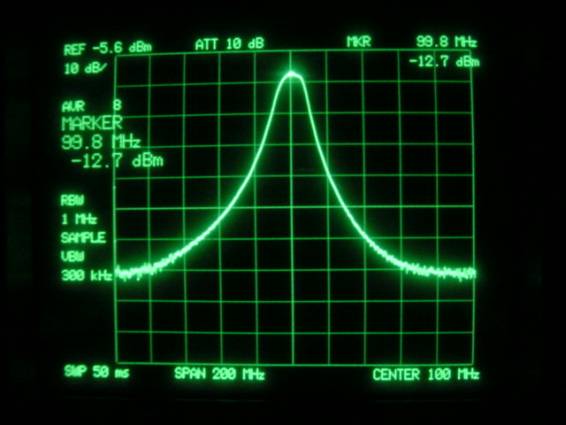

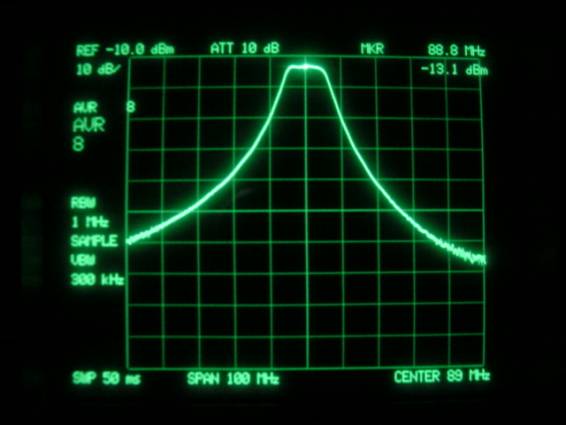

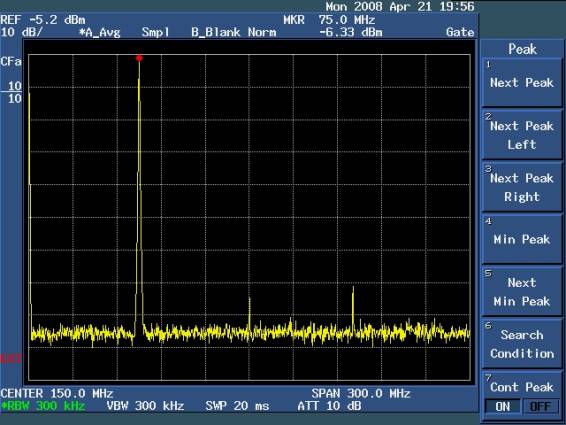

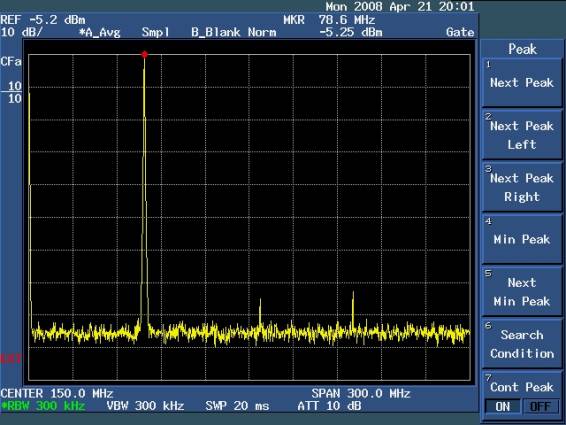

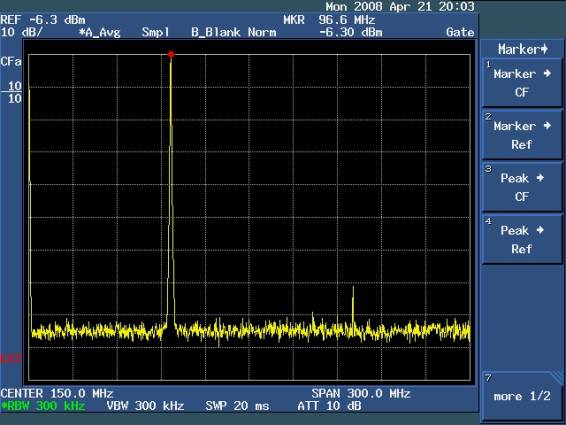

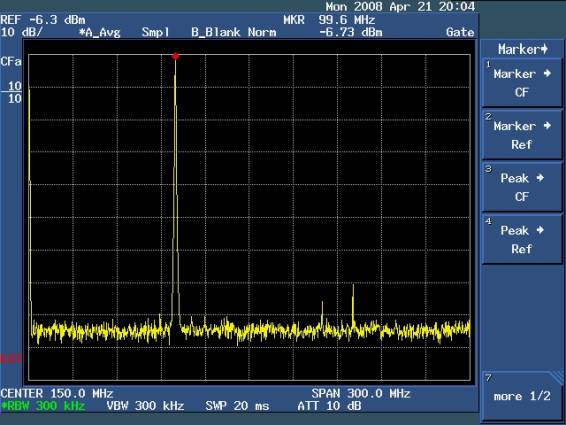

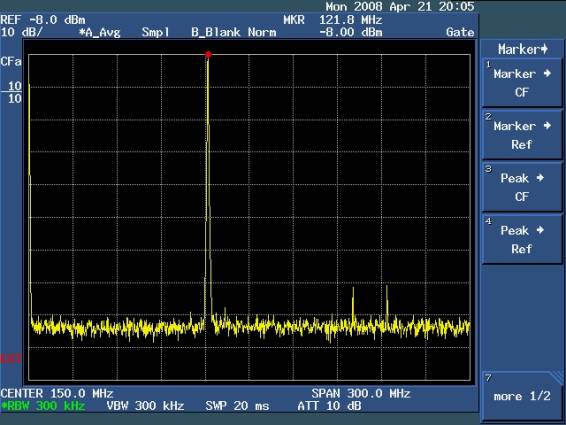

�P�T�O�l�g���o�� ���t�@�����X���g���@�S�O�O�l�g�� �Z���^�[���g���@�P�T�O�l�g�� �X�p���@�R�O�O�l�g�� �قڐ�������̎������ʂƈꏏ�ł��B |

|

|

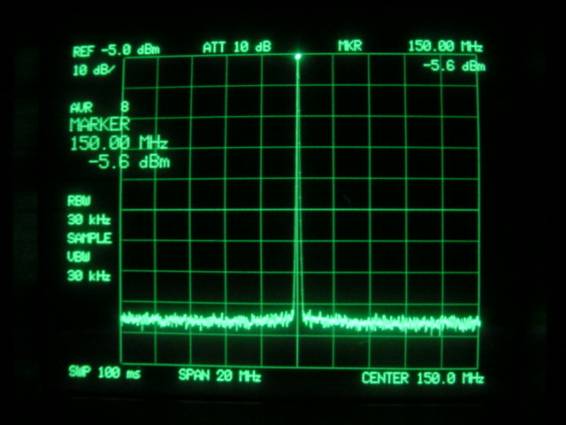

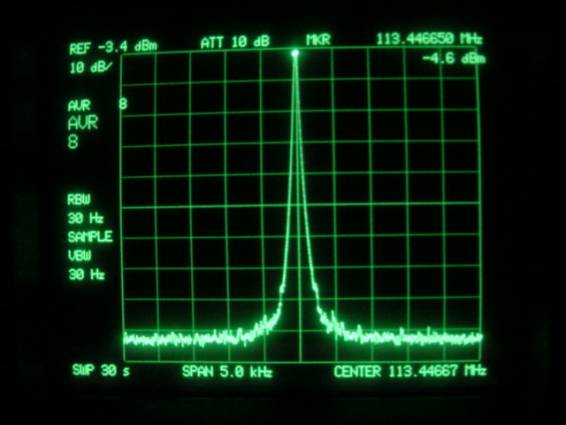

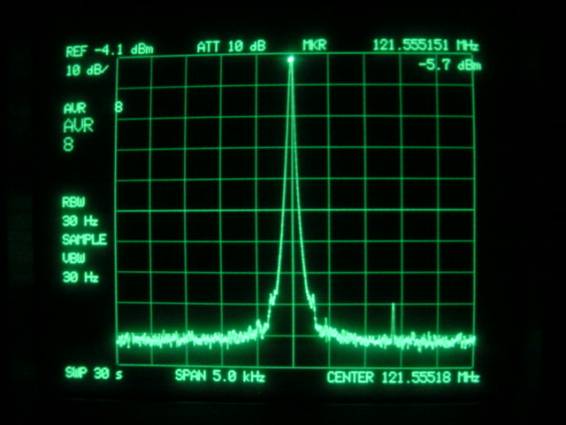

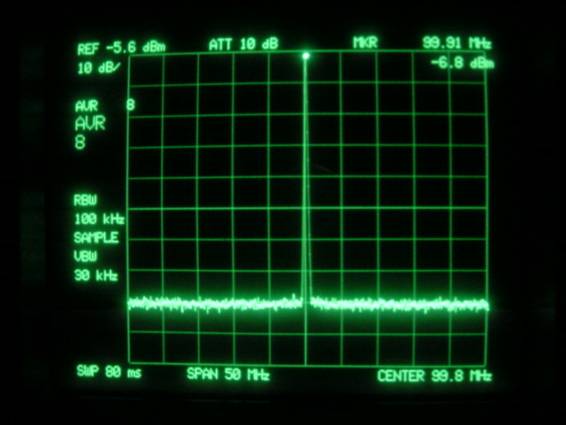

���S���g���@�P�T�O�l�g�� �X�p���@�Q�O�l�g�� |

|

|

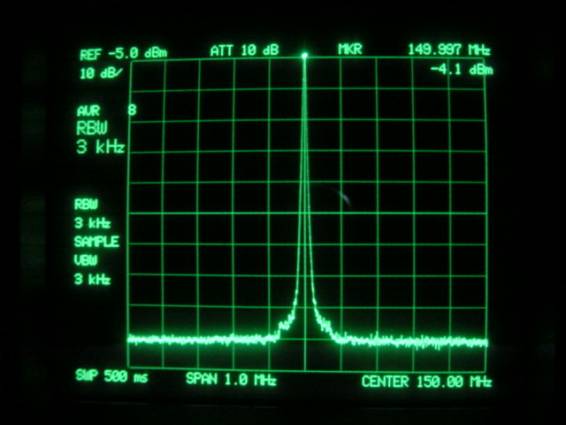

�X�p���@�P�l�g�� |

|

|

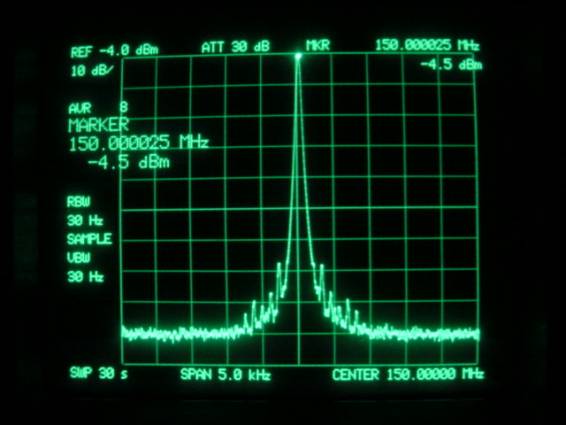

�X�p���@�T�j�g�� �ߖT�̃X�v���A�X�����Ȃ肠��܂��B ������ӂ́A��������Ƃ̘r�̍��ł��傤�B |

���t�@�����X�̂b�^�m�ƁA���o�����M���̂b�^�m�̊W�ł��B

|

|

|

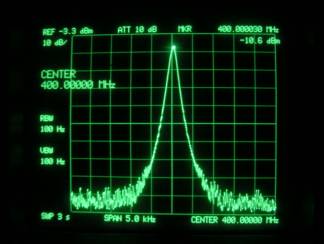

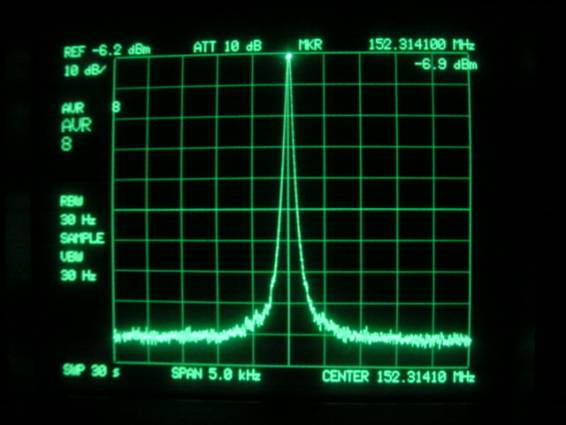

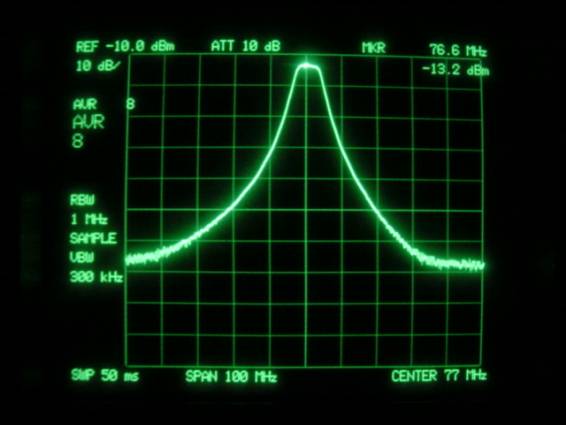

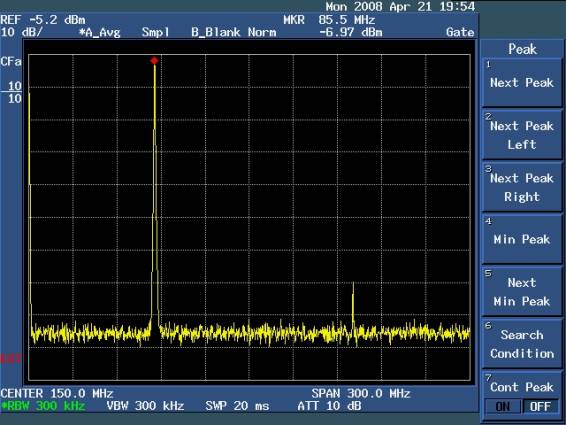

���������t�@�����X�̐M���ł��B �i�q�R�P�R�P�`��TG�o�́@�|�P�O�������j �S�O�OMH�� �E�����A���ꂽ�c�c�r�̏o�͂ł��B �P�T�OMhz |

|

|

|

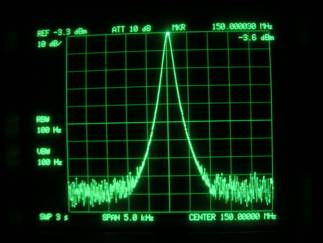

���������t�@�����X�̐M���ł��B �i�W�U�T�VB�@�|�P�O�������j �S�O�OMH�� �E�����A���ꂽ�c�c�r�̏o�͂ł��B �P�T�OMhz |

���������ƁA���t�@�����X�M���̂b�^�m���厖���Ƃ������Ƃ��ǂ�����܂��B

2008.03.06

�����́A�ׂ����N�x�Ɋ��ӂ��`�c�X�X�T�Q���`�u�q�Ő��䂵�܂����B

|

|

�`�u�q�ɂ́A�`�s���������W���A�N���b�N�Q�OMH���Ŏg���܂����B �i�����I�[�o�[�N���b�N�j �f�[�^�V�[�g��ǂ�ł݂�ƁAshiftout���߂��g���ďo�������Ȋ����������̂ŁA�v���O������g��ł݂��Ƃ��날������Ɛ���o���܂��������U���g���̐ݒ肪���܂������܂���B �����́A�ǂ����̂��܂��悭������܂���B |

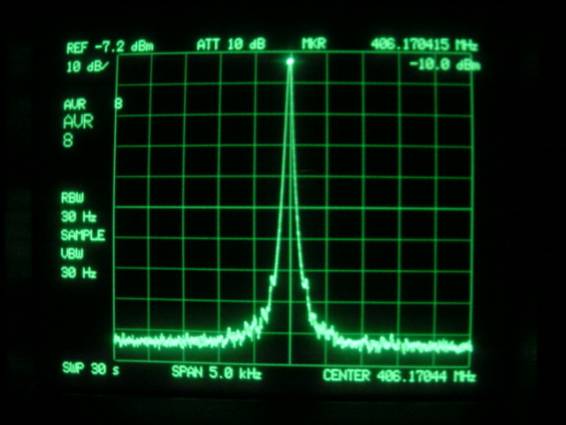

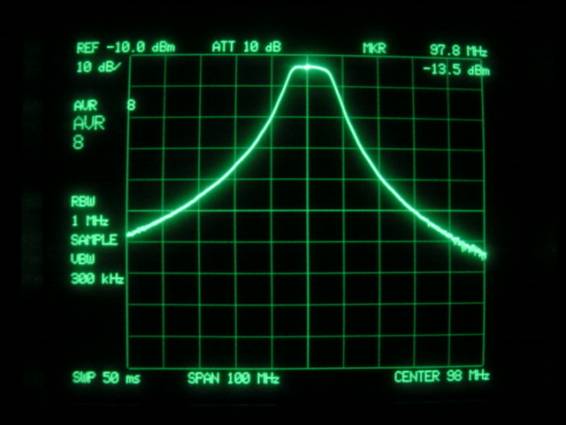

���̌�A�S�O�O�l�g���̃��t�@�����X�̎��������܂����B

|

|

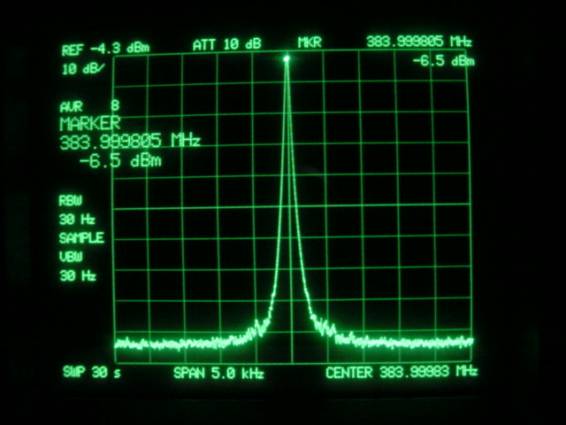

�ł����グ�����̂ł��B �F�l�ɁA����Ǝv���܂����E�E �܂��A�莝���̐����̒�����@�U�V�D�U�W�W�l�g���̐������g�� �܂����B |

|

|

���U�i�̏o�̗͂l�q�ł��B �����ōl�����̂��A��{�g���U���{���āi�U�V�D�U�W�W�l�g���~�U�j�S�O�U�D�P�Q�W�l�g�����Ƃ肾���̂� ���ݏo�Ă����U�����g�̂S�O�U�D�P�Q�W�l�g�������o���đ�������̂��ꏏ�ł͂Ȃ����Ƃ������Ƃł��B �����ŁA��̎ʐ^�̂悤�Ȃ��̂�����Ă݂܂����B �������U�̑�U�����g���a�o�e�Ŏ��o���A���o�b�Q�V�P�O�ő������a�o�e��ʂ��ĕK�v�ȐM�������o�� �Ƃ������̂ł��B |

|

|

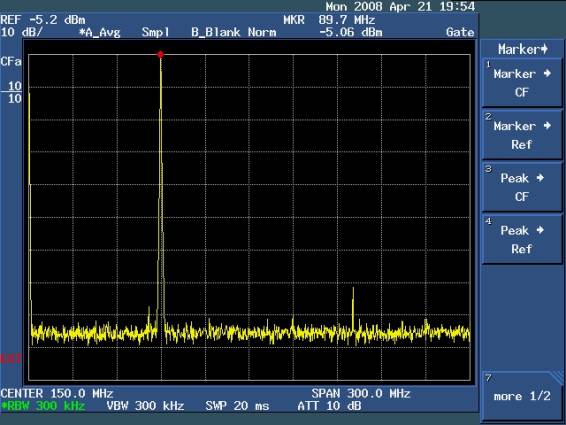

��L�̉�H�ŁA���o�����M���X�y�N�g�����ł��B �X�v���A�X�����\����܂����A��M�����͂��Ȃ艺�Ȃ̂Ŗ��Ȃ��Ǝv���Ă��܂��B |

|

|

���̏o�͂��r�o�`�m���T�j�g���Ō������ł��B �\���g�������Ȋ����ł��B |

|

|

��L�M�����A���t�@�����X�ɂ��č�����P�T�Q�l�g���̐M���ł��B �S�������Ė��Ȃ��悤�ł��B �O�̎��́A�W�U�T�V�a���M�����ł������A������ɖ�肠��� �悤�Ȋ����ł��B |

2008.03.20

|

|

���̌�A��L�̂U�{�g���o��H�ł͈��萫�ɏ�����肪 �������̂ł�����߂Ē��{��H���g�����Ƃɂ��܂����B �g���������͂U�SMH���̂R�����I�[�o�[�g�[���̂��̂ł��B ���̍������g���ł̂u�w�n�Ɍ��\��J���܂����B ���낢��ȉ�H�������Ă݂܂������A���ǂb�p�o�ŎЊ��� �u�o�k�k��H�̐v�Ɖ��p�v�̒��ɂ����H���g���܂����B �o�k�k�����́A�ȑO�P�O�l�g���̊�M����������Ƃ��̎��� ��Ղ��c���Ă��܂����̂ł���������������Ďg���܂����B �o�k�k�p�̂h�b�͂S�O�S�U���g���܂����B ���̂U�S�l�g���̐M�����~�R�~�Q���ĂR�W�S�l�g���ɂ��Ă��܂��B �T�O�l�g���܂œ���Ă��A�k�n�͂P�Q�Q�l�g���܂łł��̂ŁA���� �R�W�S�l�g���ł��\���ł��傤�B |

|

|

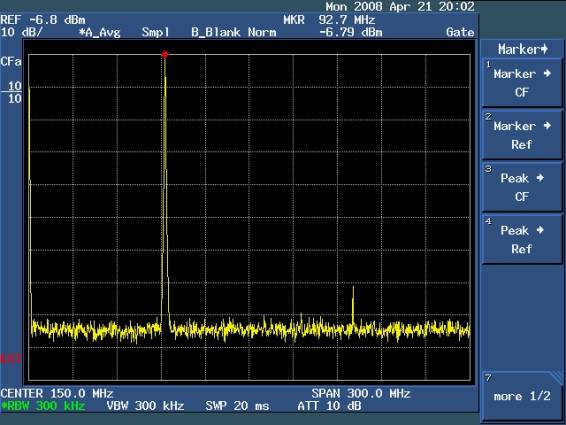

�o�͐M���ł��B ��́A�U�{�g���o�ɔ�ׂĂ��Ȃ�b�m�����P����Ă��܂��B |

|

|

���݂́A�o�̓X�v���A�X�ł����A�܂����Ȃ肠��܂��B ���̌�ɁA�a�o�e�����ĕs�v�X�v���A�X����������\��ł��B ���̃X�v���A�X���������Ă����Ȃ��ƁA��������M���ɂ��X�v���A�X����������o�Ă��܂��B |

|

|

���̌�A�a�o�e���������ăX�v���A�X��}�����܂����B |

|

|

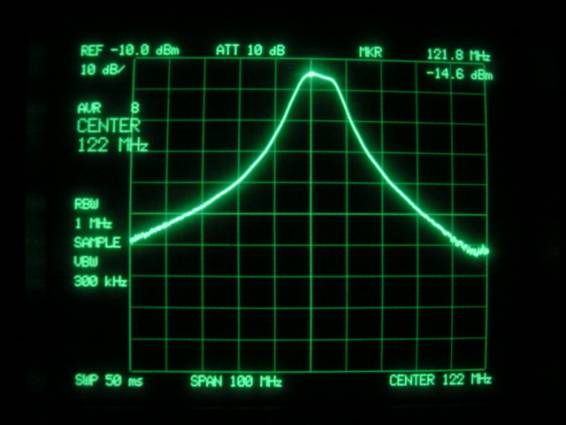

��L�M�������t�@�����X�ɂ��č�����`�c�X�X�T�Q�̏o�͂ł��B �P�P�R�l�g���Ƃ������g���ɓ��ʂȈӖ��͂���܂���B �ȑO�̂S�P�O�l�g���̃��t�@�����X�������̒萔�����̂܂� �g���Ă��邽�߂ł��B �����@�̂k�n�Ɏg���ɂ́A�S�����Ȃ��Ǝv���܂��B |

|

|

|

�o�̓X�v���A�X�̗l�q�ł��B ���t�@�����X�̃X�v���A�X�̉e���ł��Ȃ肠��܂��B �������A���ꂢ�ɂ��Ă����Ȃ��ƌ�̂a�o�e������������ɂȂ�܂��B |

�����ŋC���t�����̂ł����A�p�\�R�����琧�䂷��ꍇ�ƃ}�C�R�����琧�䂷��ꍇ�ŃX�v���A�X�̏o�������Ȃ�Ⴂ�܂��B

|

|

|

�����A�p�\�R�����琧�䂵���Ƃ� �E���A�}�C�R�����琧�䂵���Ƃ��ł��B �}�C�R�����琧�䂵���ق����X�v���A�X�� �����o�Ă��܂��B ���낢��ȃp���[�_�E���@�\������̂� �ǂꂩ���g�������̂�������܂��� �����_�ł́A�ǂ��킩��܂���B |

2008.03.27

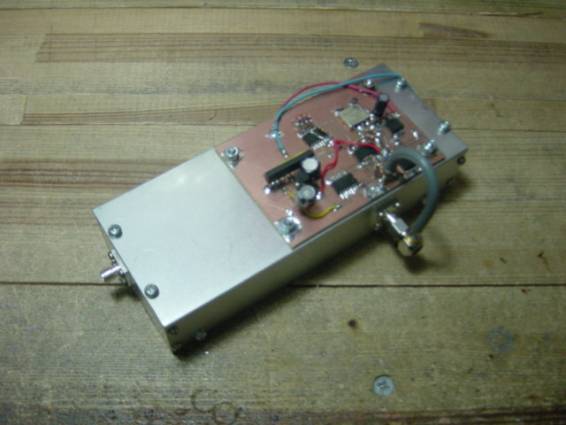

�R�W�S�l�g���̂k�n���A�����p�ɂ܂Ƃ߂܂����B

|

|

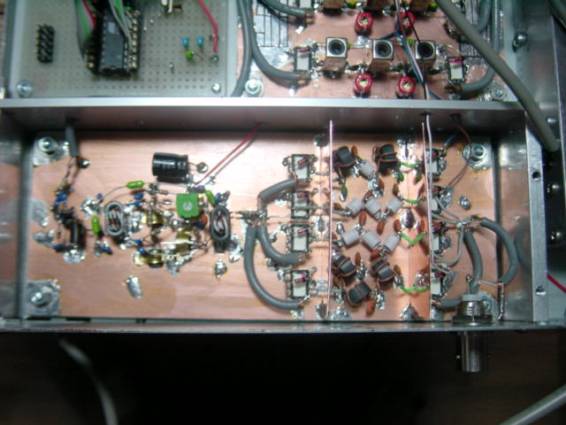

�P�[�X�̒��ɁA�u�w�n�{���{���������Ăo�k�k�����͐e�T���T�����Ŕw���ɏ悹�܂����B �o�k�k�͏����V���v���ɂ��č�芷���܂����B �o�k�k�́A�R�W�S�l�g���̏o�͂ł͂Ȃ��r���̂U�S�l�g�������o���� �g���Ă��܂��B |

|

|

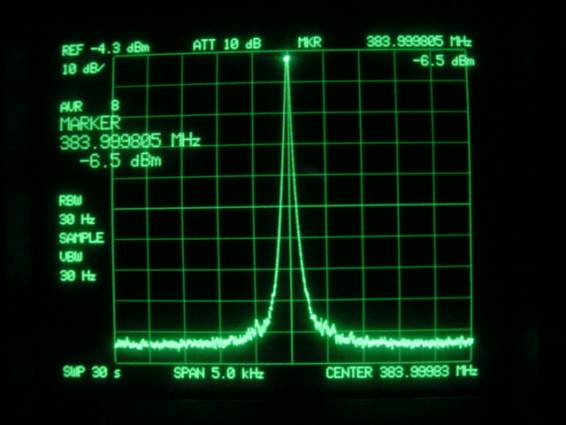

�o�̓X�y�N�g�����ł��B |

|

|

�X�v���A�X�̗l�q�ł��B ��Q�����g�������o�Ă��܂����Ƃ肠�����g���Ă݂܂��B |

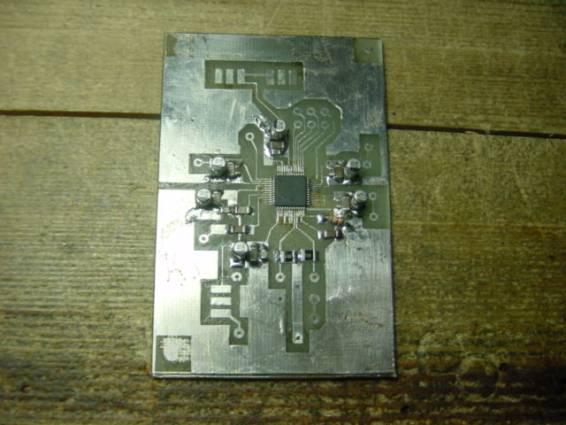

�`�c�X�X�T�Q�`�X�X�T�S�p�Ɋ�Ղ�����Ă݂܂����B

|

|

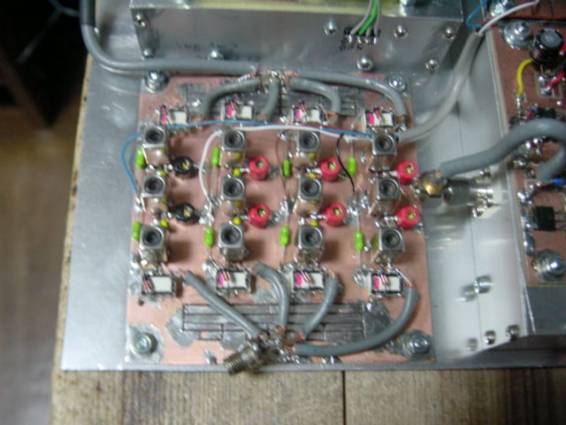

�p�^�[���͂o�b�a�d���g���A�G�|�L�V�Жʊ�Ղ̊�����Ղ� �g���č��܂����B ��Ղ̍쐬�́A���q�ւ̊O���ł��B �i�����́A������Ղ��g���Ċ�Ղ���������Ƃ�����܂���j �p�^�[���̍������܂����A �p�X�R���ނ��s���T�ɂ��܂��܂Ƃ߂��܂���ł����B ����ł��o���b�N��ՂƔ�ׂ�Ǝ�����������Ȃ������� �Ƃ������x���Ǝv���܂��B |

|

|

���̌�A�p�[�c��S���t���Ă݂��Ƃ��떳�����삵�܂����B |

|

|

�o���オ�����A�c�c�r��ՁA�R�W�S�l�g���k�n�A�`�u�q���Ȃ��� �������Ă���Ƃ���ł��B |

|

|

��L�\���ō�����P�Q�Q�D�T�T�T�l�g���̐M���ł��B ����́A�T�O�l�g���p�̂k�n���g���ɂȂ�܂��B �i�V�P�D�T�T�T�{�T�O���P�Q�Q�D�T�T�T�l�g���j �c�O�Ȃ���X�v���A�X�������܂����W�O�������Ȃ̂Ŗ�� �Ȃ��ł��傤�B |

|

|

�L���͈͂̃X�v���A�X�ł��B ���ς�炸�A�X�v���A�X���炯�ł��B �������K���Ȃ��ƂɎ�M���̋ߖT�ɂ͖ڗ������X�v���A�X�� ����܂���B �a�o�e�Ŕr���ł������ł��B |

2008.04.04

���̌�A���݂̍\���ł͂Q�W�l�g���p�̂k�n�i�X�X�D�T�U�l�g���j�M�������Ƃ��R�D�U�l�g�����ɃX�v���A�X������a�o�e�ł͂��ꂢ�ɂƂ�Ȃ��̂ō\����ς���

�݂邱�Ƃɂ��܂����B

�莝���̐����̒�����T�T�l�g���̐������g���W�{���ĂS�S�O�l�g������邱�Ƃɂ��܂����B

�ꉞ�r�f�i�W�U�T�V�a�j����S�S�O�l�g�����c�c�r�ɓ���đS�o���h�̂k�n�̋ߕӂɃX�v���A�X�����������ׂ܂������A���̍\���ł́}�P�O�l�g���̊Ԃɂ͑傫��

�X�v���A�X�͂���܂���ł����B

������ς��ē�������蒼���������ŁA�S�S�O�l�g���������܂����B

�e�o���h�̂k�n�ߕӂ̃X�v���A�X�̗l�q�ł��B

|

�o���h�@�k�n���g�� |

�r�o�`�m���Q�O�l�g�� |

�r�o�`�m���R�O�O�l�g�� |

|

�R�D�T�l �V�T�D�O�U�l�g�� |

|

|

|

�V�l �V�W�D�T�U�l�g�� |

|

|

|

�P�S�l�g�� �k�n���W�T�D�T�U�l�g�� |

|

|

|

�P�W�l�g�� �k�n���W�X�D�U�R�l�g�� |

|

|

|

�Q�P�l�g�� �k�n���X�Q�D�T�U�l�g�� |

|

|

|

�Q�S�l�g�� �k�n���X�U�D�S�T�l�g�� |

|

|

|

�Q�W�l�g�� �k�n���X�X�D�T�U�l�g�� |

|

|

|

�T�O�l�g�� �k�n���P�Q�P�D�T�U�l�g�� |

|

|

���ꂾ�ƁA���܂�傰���Ȃa�o�e�����Ȃ��Ă��X�v���A�X�͎�菜�������ł��B

|

|

���}�́A�Q�W�l�g���p�̂k�n�i�X�X�D�T�U�l�g���j�́}�P�O�l�g������ �X�v���A�X�̗l�q�ł��B �o�͂ɁA�a�o�e�����Ă��܂��B �ϑ��o����A�W�O�������܂ł͊m�F�o���܂���B |

���M���g�����Œ肵�āA�k�n�̕ω��ŃX�v���A�X���ǂ̂悤�ɕω����邩���肵�Ă݂܂����B

|

|

����A���������a�o�e�̓����ł��B �P�O�l�g������ŁA�|�P�O�����������Ă��܂��B ����A���������a�o�e�͂i�`�P�c�v�l���g�o�Ɍf�ڂ���Ă��� �a�o�e�ł��B �q�e�@�b�������������������̒��́@�a�o�e�@�b�����������������@�r�q�O�m�R�D������ ���g���܂����B ���S���g���P�O�O�l�g���@�a�v���P�O�l�g�� �k�P���k�Q���k�R���O�D�X�S���g�i�V�j�s�������@�P�O���j �b�n�P���b�n�Q���b�n�R���R�o �b�P���b�Q���R�O�o�e�i�S�O�o�e�@�g���}�j �}���������|�Q�D�V���� �R�����a�v���P�Q�l�g�� �}���������[�P�O�������炢�܂ŋ��e����Ƃ��������V���[�v�� �Ȃ�܂��������ꂭ�炢�Ŏg���܂��B |

2008.04.21

|

|

�a�o�e�����܂����B ��ւ��ɂ́A�����[���g���܂����B �i�H���Ŕ����Ă���T�Q�O�O�~�̕\�ʎ����p�j �W�o���h�ɂ��ꂼ��a�o�e�������������ł����� �@ �R�D�T�l�A�V�l �A �P�S�l�A�P�W�l�A�Q�P�l �B �Q�S�l�A�Q�W�l �C �T�O�l �̂S�O���[�v�ɕ����Ăa�o�e�́A�S�ōς܂����Ƃɂ��܂����B ���̂��̂̒萔�́A�q�e�@�b�������������������̒��́@�a�o�e�@�b�����������������@�r�q�O�m�R�D���������g���Čv�Z���Ă��܂��B �R�C���͂��ׂāA�V�j�s�������̃{�r�����g���Ă��܂��B |

|

|

�R�D�T�l�A�V�l �ʉߑш�@�V�T�l�|�V�X�l |

|

|

�P�S�l�C�P�W�l�A�Q�P�l �ʉߑш�@�W�T�l�|�X�R�l |

|

|

�Q�S�l�A�Q�W�l �ʉߑш�@�X�U�l�|�P�O�P�l |

|

|

�T�O�l �ʉߑш�@�P�Q�P�l�|�P�Q�R�l �����ɁA���������X�v���A�X������̂ʼn��̃G�b�W�Ɏ����Ă��� ���܂��B |

|

|

�R�D�T�l�p�k�n |

|

|

�V�l�g�p�k�n |

|

|

�P�S�l�g���p�k�n |

|

|

�P�W�l�g���p�k�n |

|

|

�Q�P�l�g���p�k�n |

|

|

�Q�S�l�g���p�k�n |

|

|

�Q�W�l�g���p�k�n |

|

|

�T�O�l�g���p�k�n |

�������g���ɏ����X�v���A�X���c���Ă��܂����A���̌�Ɂ{�Q�O�������܂ő�������A���v��t�������ƁA�Ō�ɂ��ꂢ�ɂ������ł��B

2008.05.05

|

|

���̓x�́A�s�q�w�͂ǂ�ȃP�[�X�ɓ���悤���Y�� �b�`�s�u�p�̃`���[�i�[�̃P�[�X�𗘗p���ĂS�ɕ����� ��邱�Ƃɂ��܂����B �܂��͂k�n���������Ă݂܂����B ���σp�l�����܂��ł��̂ŊԔ����ʂł��B �����P�[�X�ɁA�d���E�q�e�E�h�e���܂Ƃ߂Ă݂܂��B �`�u�q�̃v���O�����́A�܂��c�c�r����A�a�o�e��ւ��A�k�b�c�\�� �V�������\���A�r�s�d�o��ւ������ł����A��W�O���̃v���O�����G���A���g���Ă��܂��܂����B�c��Q�O���łq�h�s�A�u�e�n��ւ������ꍞ�߂邩�����ȂƂ���ł��B |

|

|

�����A���p���邱�Ƃɂ����b�`�s�u�`���[�i�[�ł��B �u�b���������@�m�������������@�b���������v�̂��̂ł��B �ȑO���t�I�N�ŁA�����������S����ƂV�䂠���܂��Ƃ����̂� ����܂��đ����Ă���������̂ł��B ���̃V���[�V�͓S�ł�����W�̓v���X�`�b�N�Ȃ̂ŃV�[���h ���ʂ��H�H�Ȃ̂ł�����肠��������Ă݂܂��B |

|

|

|

|

|

�����̗l�q�ł��B �����̍����W�����Ă���̂��o�`�����ł��B �����Ł{�Q�O�������܂ő������܂��B ��ԉE���A�S�S�O�l�g�����t�@�����X�M�� ���̉E���A�c�c�r���U�� ���̉E���A�a�o�e �`�u�q�́A�`�s�X�O�r�W�T�R�T�łc�c�r����A�k�b�c�\���A�a�o�e��ւ� �`�s���������W�łV�������\�������Ă��܂��B |

|

|

�{�Q�O�������o�`�̒��ł��B �m�e�a�`�����ƁA���A�҂̂��������J�X�P�[�h�o�o��H�ł��B ���̉�H�́A�P�X�W�O�N�R�����́u�T�O�l�g���r�r�a�g�����V�[�o�� �v�E����v�̒��̉�H���Q�l�ɂ��܂����B �Ō�ɂk�o�e��ʂ��ďo�͂��Ă��܂��B �s���́u�Q�r�b�R�R�T�T�v���g���Ă��܂��B �����M���Ȃ�̂ŁA���M�Ƌz���̋��x�⋭�����˂Ċ�Ղɐ^�J�ŌŒ肵�Ă��܂��B �P�{������A��T�O���`�����Ă��܂��B |

|

|

�Q�P�l�g���p�̂k�n�@�X�Q�D�T�U�l�g�����o�͂����Ƃ��̃X�v���A�X�̗l�q�ł��B ���̑��̃o���h���A�X�v���A�X�͂ɂ���������ł��B �X�v���A�X����c���Ă��܂����A�ގ����邩�ǂ����͍ŏI�����̎��ɔ��f���邱�Ƃɂ��܂��B |